## Høgskulen på Vestlandet

### Bacheloroppgaue

ELE350

| Startdato:                                                                                                | 08-05-2023 09:00 CEST                                                 | Termin:            | 2023 VÅR                                    |  |

|-----------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|--------------------|---------------------------------------------|--|

| Sluttdato:                                                                                                | 22-05-2023 14:00 CEST                                                 | Vurderingsform:    | Norsk 6-trinns skala (A-F)                  |  |

| Eksamensform:                                                                                             | Bacheloroppgave                                                       |                    |                                             |  |

| Flowkode:                                                                                                 | 203 ELE350 1 O 2023 VÅR                                               |                    |                                             |  |

| Intern sensor:                                                                                            | Eirik Haustveit                                                       |                    |                                             |  |

| Deltaker                                                                                                  |                                                                       |                    | Informasjon fra deltaker                    |  |

| Navn:                                                                                                     | Eirik Skorve Haugland                                                 |                    | Egenerklæring *: Ja                         |  |

|                                                                                                           |                                                                       |                    | Inneholder besvarelsen Nei<br>konfidensielt |  |

| Kandidatnr.:                                                                                              | 234                                                                   |                    | materiale?:                                 |  |

| HVL-id:                                                                                                   | 591371@hul.no                                                         |                    | <b>Jeg bekrefter at jeg har</b> Ja          |  |

|                                                                                                           |                                                                       |                    | registrert<br>oppgavetittelen på            |  |

|                                                                                                           |                                                                       |                    | norsk og engelsk i                          |  |

|                                                                                                           |                                                                       |                    | StudentWeb og vet at                        |  |

|                                                                                                           |                                                                       |                    | denne vil stå på<br>vitnemålet mitt *:      |  |

|                                                                                                           |                                                                       |                    |                                             |  |

| Gruppe<br>Gruppenavn:<br>Gruppenummer:<br>Andre medlemmer i                                               | BO23EB-42<br>5<br>Inorid Houland Marius Midtha Fr                     | nglund             |                                             |  |

| Gruppenavn:                                                                                               | 5                                                                     | nglund             |                                             |  |

| Gruppenavn:<br>Gruppenummer:<br>Andre medlemmer i<br>gruppen:                                             | 5                                                                     |                    | *                                           |  |

| Gruppenavn:<br>Gruppenummer:<br>Andre medlemmer i<br>gruppen:<br>eg godkjenner a                          | 5<br>Ingrid Hovland, Marius Midtbø Er                                 |                    | *                                           |  |

| Gruppenavn:<br>Gruppenummer:<br>Andre medlemmer i<br>gruppen:<br>eg godkjenner a                          | 5<br>Ingrid Hovland, Marius Midtbø Er                                 |                    | *                                           |  |

| Gruppenavn:<br>Gruppenummer:<br>Andre medlemmer i<br>gruppen:<br>eg godkjenner a<br>Ja<br>Er bacheloroppg | 5<br>Ingrid Hovland, Marius Midtbø Er                                 | cheloroppgaven min |                                             |  |

| Gruppenavn:<br>Gruppenummer:<br>Andre medlemmer i<br>gruppen:<br>eg godkjenner a<br>Ja                    | 5<br>Ingrid Hovland, Marius Midtbø Er<br>uvtalen om publisering av ba | cheloroppgaven min |                                             |  |

| Gruppenavn:<br>Gruppenummer:<br>Andre medlemmer i<br>gruppen:<br>eg godkjenner a<br>Ja<br>Er bacheloroppg | 5<br>Ingrid Hovland, Marius Midtbø Er<br>uvtalen om publisering av ba | cheloroppgaven min |                                             |  |

| Gruppenavn:<br>Gruppenummer:<br>Andre medlemmer i<br>gruppen:<br>eg godkjenner a<br>Ja<br>Er bacheloroppg | 5<br>Ingrid Hovland, Marius Midtbø Er<br>uvtalen om publisering av ba | cheloroppgaven min |                                             |  |

| Gruppenavn:<br>Gruppenummer:<br>Andre medlemmer i<br>gruppen:<br>eg godkjenner a<br>Ja<br>Er bacheloroppg | 5<br>Ingrid Hovland, Marius Midtbø Er<br>uvtalen om publisering av ba | cheloroppgaven min |                                             |  |

# 3-phase DC/AC converter with SV-PWM

Marius Englund Eirik Skorve Haugland Ingrid Hovland

Bachelor of Science in Electric Power Engineering Submission date: May 2023 Supervisor: Eirik Haustveit

Western Norway University of Applied Sciences Faculty of Engineering and Science Department of Computer Science, Electrical Engineering and Mathematical Sciences

A DC-to-AC converter development project.

## **Document** Control

| Report title (English):               | Date/Version:     |

|---------------------------------------|-------------------|

| 3-phase DC/AC converter with SV-PWM   | 22  May  2023/2.0 |

| Report title (Norwegian):             | Report no.:       |

| 3-fase DC/AC-omformar med SV-PWM      | BO23EB-42         |

| Authors:                              | Study program:    |

| Marius Englund                        | Power Engineering |

| Eirik Skorve Haugland                 | Number of pages   |

| Ingrid Hovland                        | w/appendices:     |

|                                       | 186               |

| University's supervisor:              | Grading:          |

| Eirik Haustveit                       | Open              |

| Remarks:                              |                   |

| We allow this thesis to be published. |                   |

| Employer:                                     | Employer's reference: |

|-----------------------------------------------|-----------------------|

| Western Norway University of Applied Sciences | Eirik Haustveit       |

| Employer's contact:                           |                       |

| Eirik Haustveit — ehau@hvl.no                 |                       |

| Revision | Date        | Description             | Executed by    |

|----------|-------------|-------------------------|----------------|

| 0.1      | 11 Jan 2023 | Prepared LaTeX template | Marius Englund |

| 1.0      | 06 Feb 2023 | Submitted pre-project   | The Authors    |

| 2.0      | 22 May 2023 | Submitted final draft   | The Authors    |

## Preface

This project, titled "3-phase DC/AC converter with SV-PWM", was conducted at the Western Norway University of Applied Sciences (HVL), Department of Computer Science, Electrical Engineering and Mathematical Sciences during the spring semester of 2023.

As the authors of this thesis, we are pleased to present the culmination of our academic journey towards obtaining a Bachelor's degree in Electric Power Engineering. The project was initiated by a lecture we attended during the fall semester of 2022, which presented a compelling topic that sparked our interest.

Over the course of several months, we have dedicated ourselves to research, experimentation, and analysis in order to develop a comprehensive understanding of power converter technologies and their applications in the contemporary power industry. It has been a challenging undertaking, but we were motivated to ensure that our objectives were met.

We hope that this report will serve as a valuable resource for those who are interested in the field, and we encourage further development of the provided resources.

Despite utilizing tools to improve the academic tone of the report, we unequivocally declare that this thesis, along with the research presented within it, are entirely original and the result of our own efforts.

Bergen, 22 May 2023

Marius Énglund

M. Einle Shore Houghard

Eirik Skorve Haugland

Ingrid Hovland

## Acknowledgements

We offer our profound appreciation to our supervisor, Eirik Haustveit, for your outstanding efforts in assisting and guiding us throughout the course of the project. Your dedication and mastery of the subject matter have been invaluable in ensuring the successful completion of our work.

Additionally, we would like to acknowledge Vegard Steinsland for your valuable advice during the project, as well as the generous loan of your rectifier. We would also like to thank Farzan Jouleh for your assistance in procuring the necessary components, and Endre Håland for your help in ordering the circuit board.

Furthermore, we wish to express our gratitude to the faculty and lecturers at HVL for providing us with a challenging yet rewarding academic environment. This has enabled us to navigate the complexities of our chosen field.

Lastly, we want to recognize our classmates at HVL for the experiences we have shared together over the past three years. We wish you all the best as you embark on the next chapter of your careers.

> M. Englund E. S. Haugland I. Hovland

### Abstract

Electric motors are indispensable in modern industries and are utilized in a wide range of applications that impact various aspects of our daily lives. Motor drives are responsible for nearly two-thirds of the world's total energy consumption, highlighting the importance of developing energy-efficient control techniques. Pulse Width Modulation (PWM) enable the regulation of speed and torque of AC machines and can contribute significantly to the energy efficiency of motor applications. This bachelor's thesis presents the development of a three-phase two-level DC-to-AC converter that utilizes Space Vector Pulse Width Modulation (SV-PWM) to control the induction machine.

The work presented in the thesis investigates the interdependence between theoretical principles of motor control and circuit board design, encompassing aspects such as components selection, code development, and simulation. An essential aspect of the project involves developing a quality control method to ensure the circuit board's reliability and functionality. Laboratory experiments are conducted to evaluate the design's effectiveness in real-world scenarios, comparing two modulation techniques while the circuit board is connected to both resistive and inductive loads.

After conducting a series of tests on the converter with the aim of resolving issues and enhancing its design, the outcomes have demonstrated a circuit board that is operational and adheres to its specified functional description. The laboratory experiments confirmed the correspondence between theory and practice, and verified the converter's ability to control the induction machine. In line with the employer's requirements, the results indicate that the design is suitable for use in future educational laboratory experiments.

To augment the converter's usefulness as an educational tool, it is advisable to implement

multiple modulation algorithms and examine compatibility with other motor categories. A major expansion could involve making the converter bidirectional, allowing for power conversion in generator operation. For further details, please refer to the chapter on Suggestions for Further Work.

> **Keywords:** Space Vector Pulse Width Modulation, SV-PWM, Sinusoidal Pulse Width Modulation, SPWM, inverter, PCB design, motor drives

## Samandrag

Elektriske motorar har ei avgjerande rolle i moderne industri og vert brukt i eit breitt spekter av applikasjonar som påverkar ulike aspekt av kvardagen vår. Motordrifter er ansvarlege for nærmare to tredjedelar av verdas totale energiforbruk, noko som understrekar viktigheita av å utvikle energieffektive teknikkar for å styre dei. Pulsbreiddemodulasjon (PWM) gjer det mogleg å regulere både hastigheita og dreiemomentet til vekselstraumsmaskiner, og kan dermed bidra til å energieffektivisere motorapplikasjonar. Denne bacheloroppgåva presenterer utviklinga av ein trefasa tonivå likestraum-til-vekselstraum-omformar som nyttar romvektormodulasjon (SV-PWM) for å kontrollere induksjonsmaskina.

Arbeidet som presenterast i oppgåva utforskar samanhengen mellom teoretiske prinsipp for motorstyring og krinskortdesign, inkludert prosessar som val av komponentar, kodeutvikling og simulering. Ein viktig del av prosjektet involverer utviklinga av ein kvalitetskontrollmetode for å sikre pålitelegheit og funksjonalitet til krinskortet. Laboratorieeksperiment blir utførte for å evaluere effektiviteten til designet i reelle situasjonar, der to ulike modulasjonsteknikkar blir samanlikna medan krinskortet er tilkopla både resistiv og induktiv belastning.

Etter å ha gjennomført ei rekkje testar på omformaren med mål om å rette feil og forbetre designet, viste resultata eit fungerande krinskort som oppfylte si angitte funksjonsbeskriving. Laboratorieforsøka stadfesta samsvaret mellom teori og praksis, og verifiserte omformarens evne til å styre induksjonsmaskina. I tråd med oppdragsgjevarens ynskjer, fastslår resultata at designet eigna seg for bruk i framtidige utdanningsrelaterte laboratorieeksperiment.

For å auke nytteverdien av omformaren som eit opplæringsverktøy, ville det vere føremålstenleg å implementere fleire modulasjonsalgoritmar, samt undersøkje kompatibiliteten med andre motorkategoriar. Ei større utviding kan vere å gjere omformaren støttande for effektflyt i begge retningar, slik at den også kan brukast som kraftomformar i generatordrift. For fleire detaljar visast det til kapittelet om *Forslag til Vidare Arbeid*.

Nøkkelord: romvektormodulasjon, SV-PWM, sinusforma pulsbreiddemodulasjon, SPWM, vekselomformar, krinskortdesign, motordrifter

## Contents

|          | Document Control                        | i        |

|----------|-----------------------------------------|----------|

|          | Preface                                 | ii       |

|          | Acknowledgements                        | iii      |

|          | Abstract                                | iv       |

|          | Samandrag (Norwegian)                   | vi       |

|          | Contents                                | viii     |

| In       | ntroduction                             | 1        |

| Ι        | Theory                                  | 5        |

| 1        | Induction Machines and Operation        | 6        |

|          | 1.1 Electrical Model                    | 6        |

|          | 1.2 Speed and Torque Control            | 8        |

|          | 1.3 Generator Mode Operation            | 11       |

| <b>2</b> | Power Conversion with PWM               | 15       |

| 4        | 2.1 Three-Phase Two-Level Inverters     | 15<br>15 |

|          | 2.2 Sinusoidal Pulse Width Modulation   | 19       |

|          | 2.3 Space Vector Pulse Width Modulation | 25       |

|          |                                         |          |

| II       | I Development                           | 34       |

|          | -                                       |          |

| 3        | Demands and Specifications              | 35       |

|          | 3.1 Design Requirements                 | 35       |

|          | 3.2 Documentation                       | 37       |

| 4        | Problem Analysis                        | 38       |

|          | 4.1 Components Selection                | 38       |

|          | 4.2 Software Tools                      | 41       |

|          | 4.3 Laboratory Equipment                | 41       |

|          | 4.4 Proposed Solution                   | 43       |

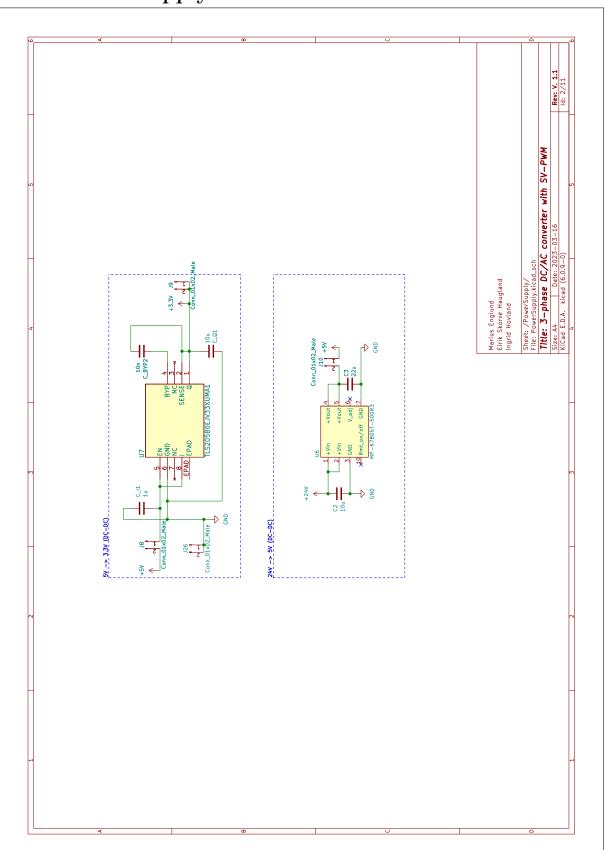

| <b>5</b> | Circuit Board Design                    | 44       |

|          | 5.1 Power Supply Selection              | 44       |

|          | 5.2 Design of Subcircuits               | 47       |

|          | 5.3 DC-Link Capacitors                  | 56       |

|          | 5.4 PCB Topology Optimization           | 60       |

| 6            | Temperature Control6.1Thermal Dissipation Analysis6.2Thermal Calculations                                                                                                                                                                                                              | <b>64</b><br>64<br>72                                                                                   |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|

| 7            | Software Development7.1Abstraction Layers7.2Timer Parameters7.3Implementation of Modulation Algorithms                                                                                                                                                                                 | <b>75</b><br>75<br>76<br>78                                                                             |

| II           | I Laboratory Experiments                                                                                                                                                                                                                                                               | 86                                                                                                      |

| 8            | Laboratory Testing8.1Elementary Function Tests8.2Motor Operation Tests                                                                                                                                                                                                                 | <b>87</b><br>87<br>97                                                                                   |

| 9            | Results Analysis9.1Discussion of Fundamental Tests9.2Impact of Varying Gate Resistors9.3Comparison of Modulation Algorithms                                                                                                                                                            | <b>102</b><br>102<br>104<br>106                                                                         |

| Di           | iscussion and Conclusion                                                                                                                                                                                                                                                               | 111                                                                                                     |

| Su           | <b>uggestions for Further Work</b> 9.4Circuit Board Design9.5Simulations9.6Software Development9.7Laboratory Experiments                                                                                                                                                               | <ul><li>113</li><li>113</li><li>115</li><li>115</li><li>116</li></ul>                                   |

| $\mathbf{A}$ | ppendices                                                                                                                                                                                                                                                                              | Ι                                                                                                       |

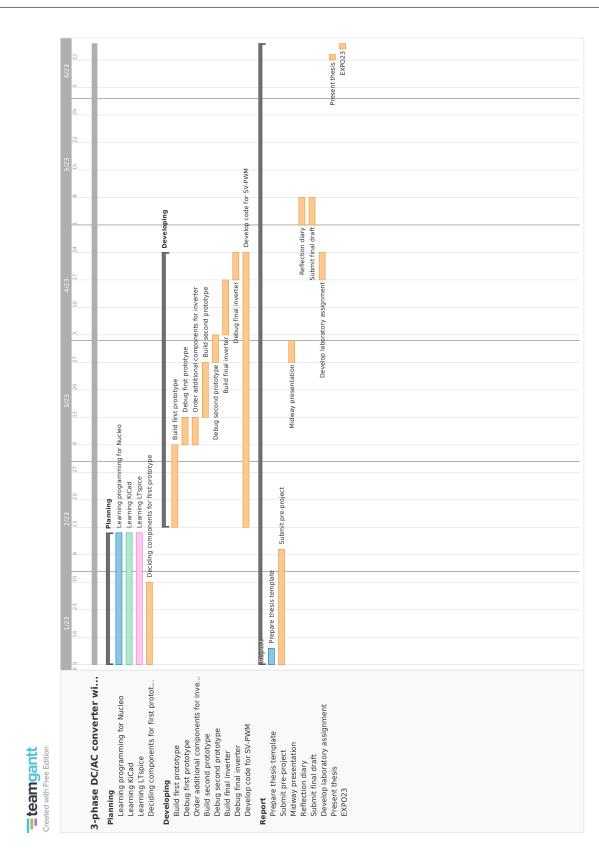

| A            | Project Management         A.1 Team Coordination         A.2 Predicted Time Schedule         A.3 Actual Time Schedule                                                                                                                                                                  | II<br>III<br>IV<br>V                                                                                    |

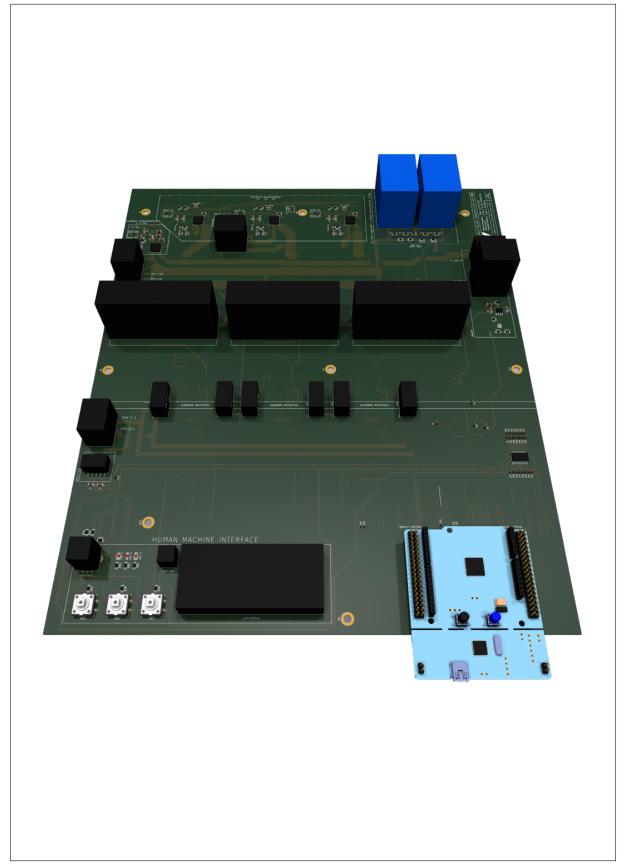

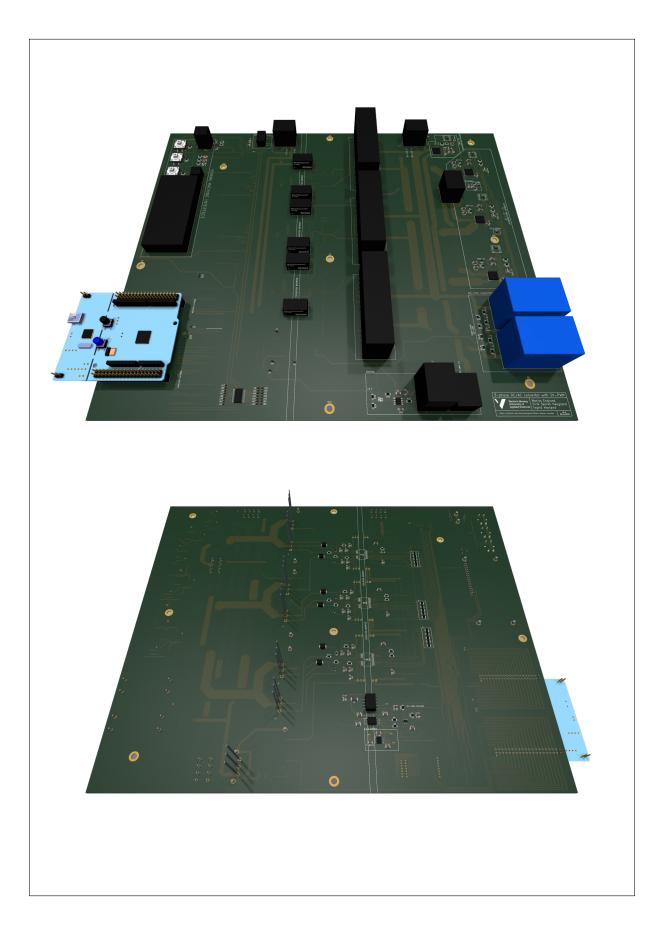

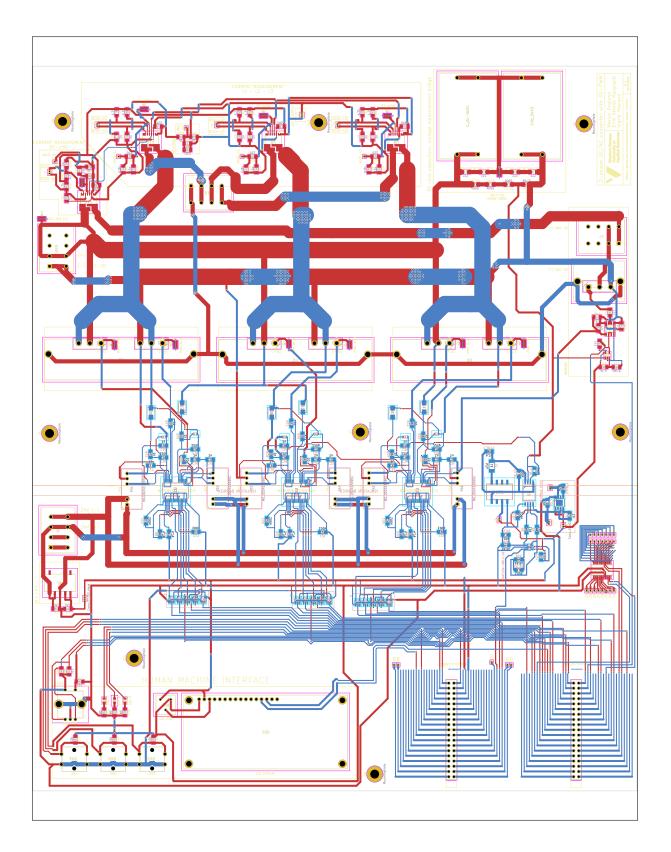

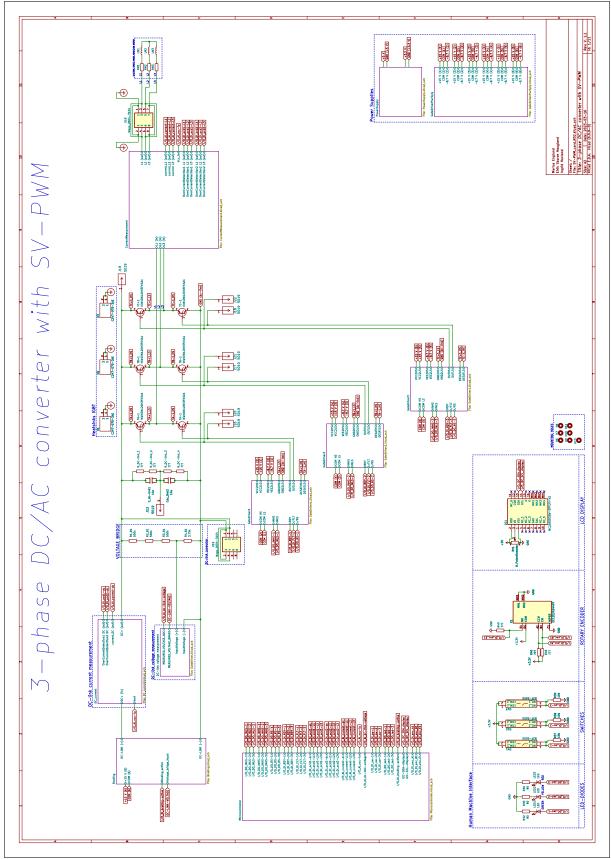

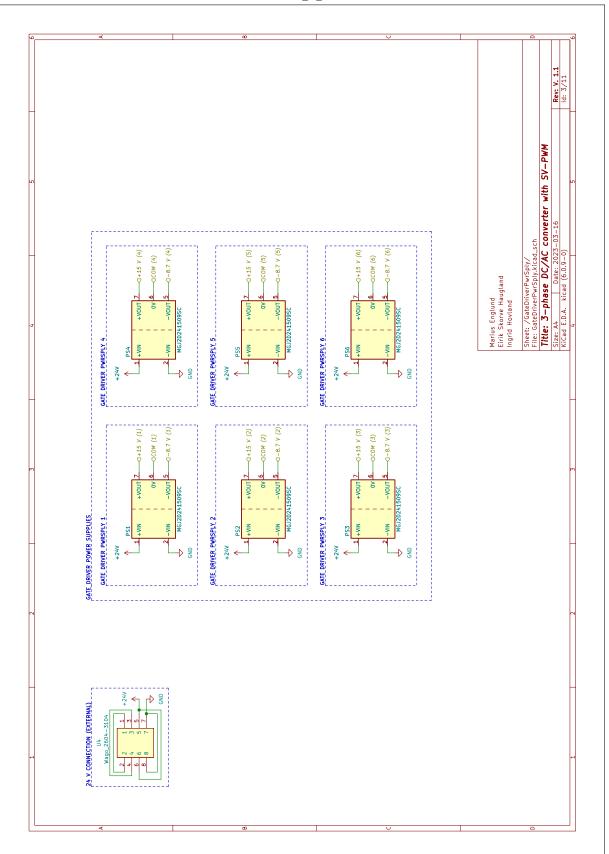

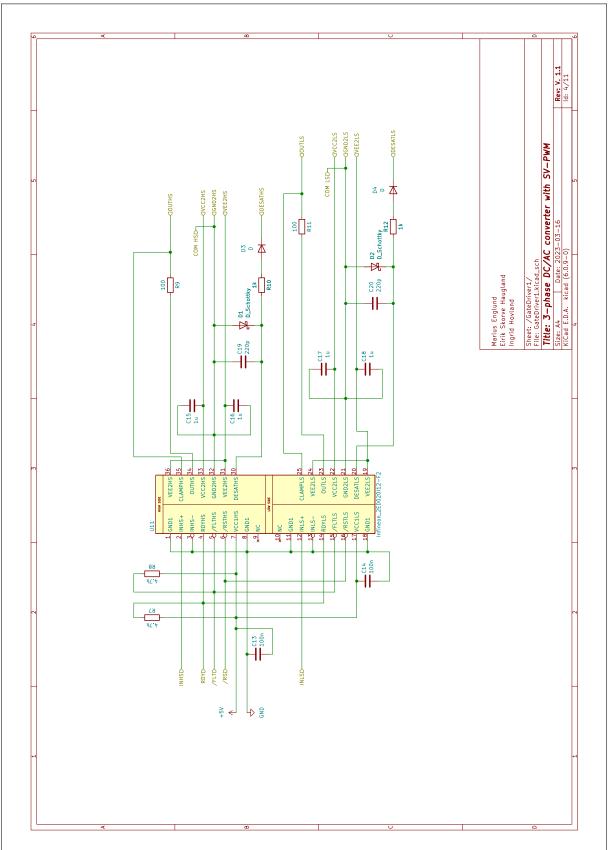

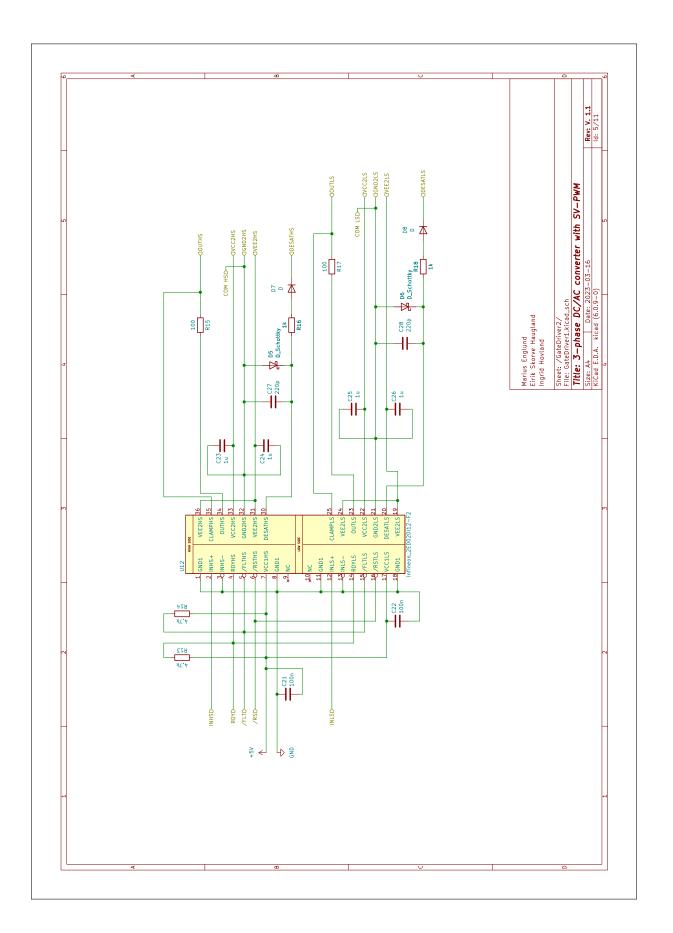

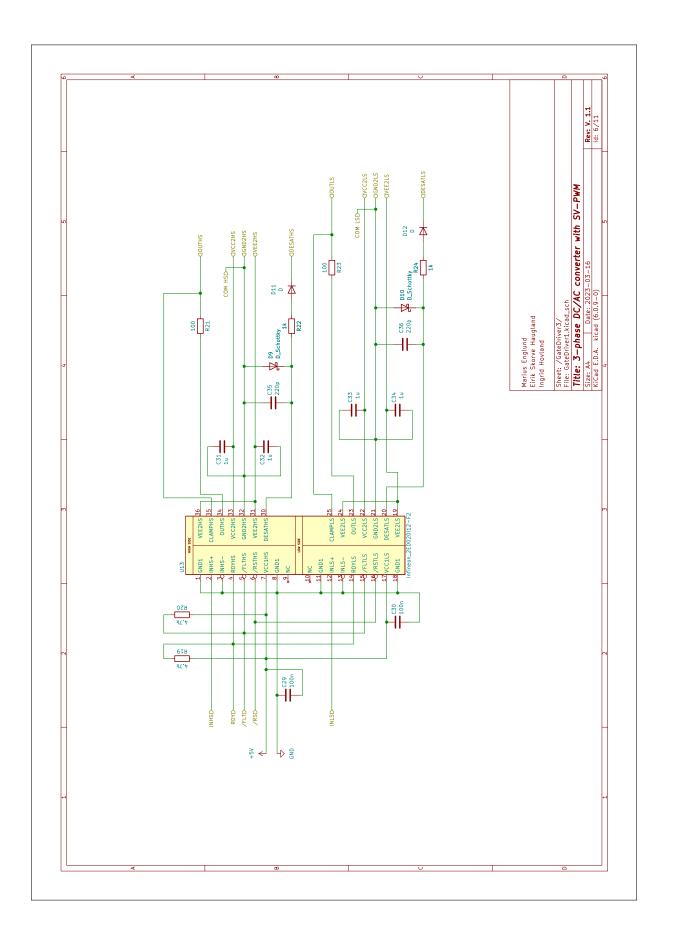

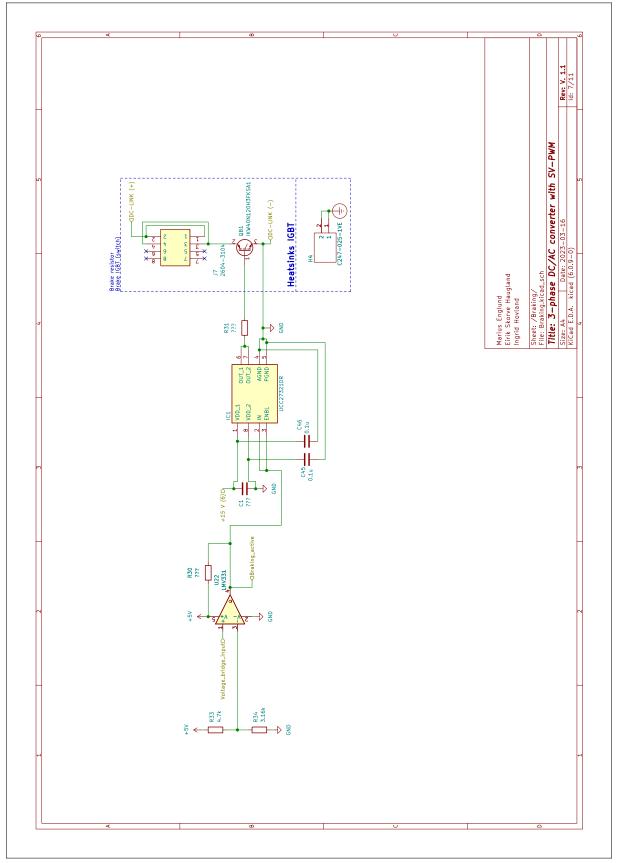

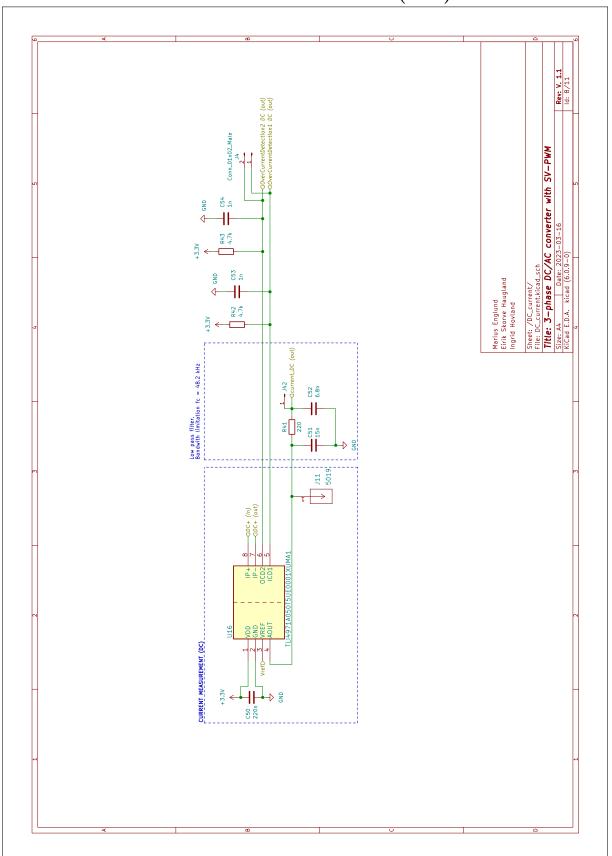

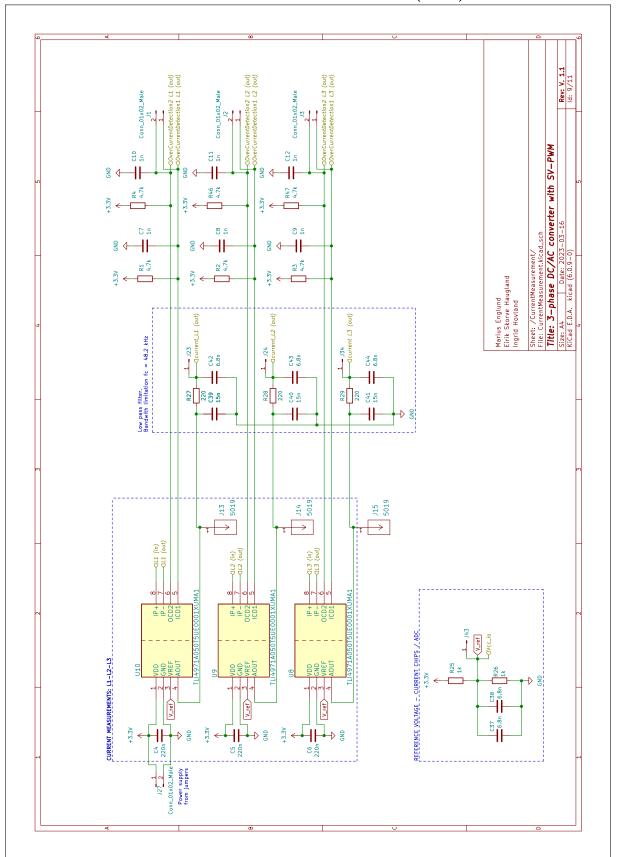

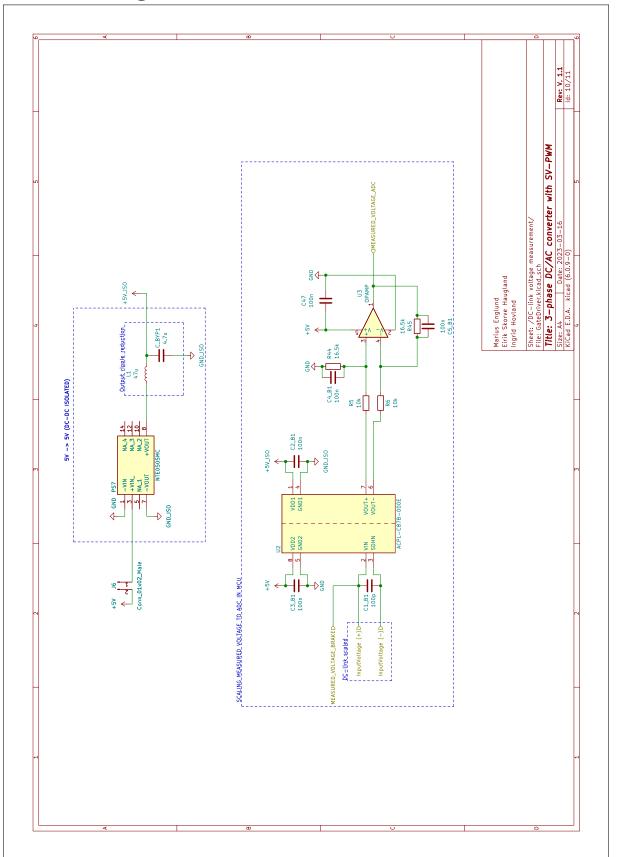

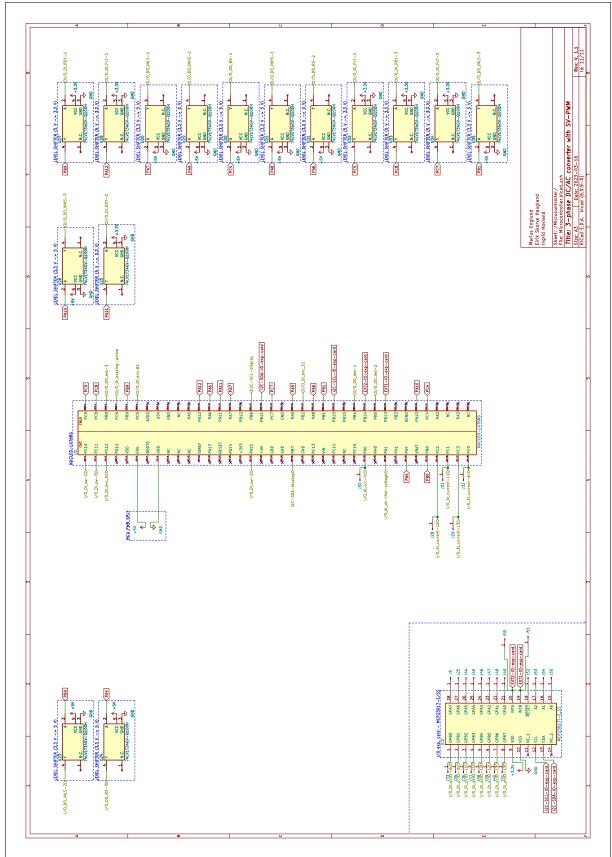

| В            | Circuit Board DesignB.1Visual Proof of ExecutionB.23D-ModelsB.3PCB LayoutB.4PCB TopologyB.5Power Supply CircuitB.6Gate Driver Power SuppliesB.7Gate Driver CircuitsB.8Braking CircuitB.9Current Measurement Circuit (DC)B.10Current Measurement CircuitA.11Voltage Measurement Circuit | VI<br>VIII<br>VIII<br>XII<br>XIII<br>XIII<br>XIV<br>XV<br>XV<br>XV<br>XV<br>XV<br>XV<br>XV<br>XX<br>XXI |

| B.12 Microcontroller CircuitXXIB.13 List of ComponentsXXIIB.14 Deviation Log PCBXXVIB.15 Design Flaws PCBXXIIB.16 DC-Link Capacitor CalculationsXXII | I<br>I<br>X |

|------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| C Source Code XXX                                                                                                                                    | I           |

| C.1 Sinusoidal PWM Algorithm                                                                                                                         | Ι           |

| C.2 Space Vector PWM Algorithm                                                                                                                       |             |

| C.3 Deviation Log MCU                                                                                                                                | V           |

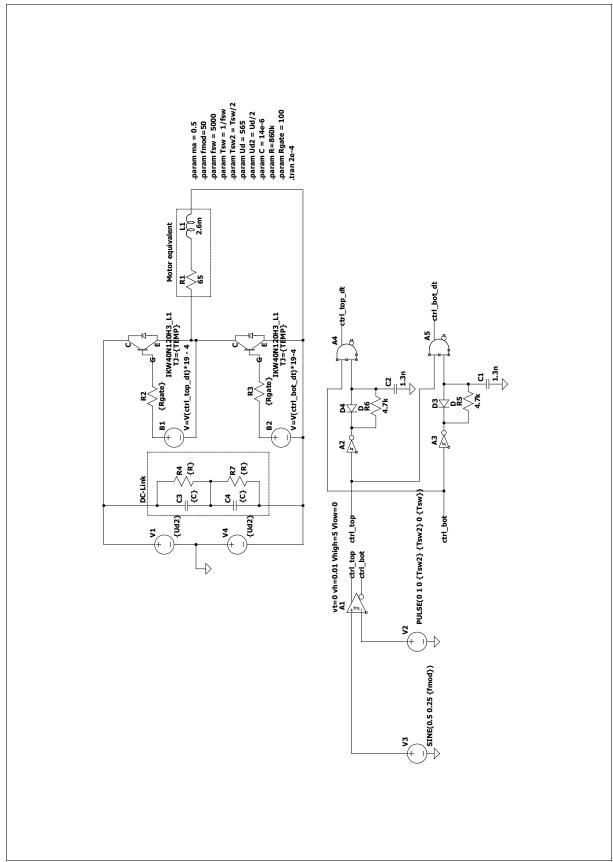

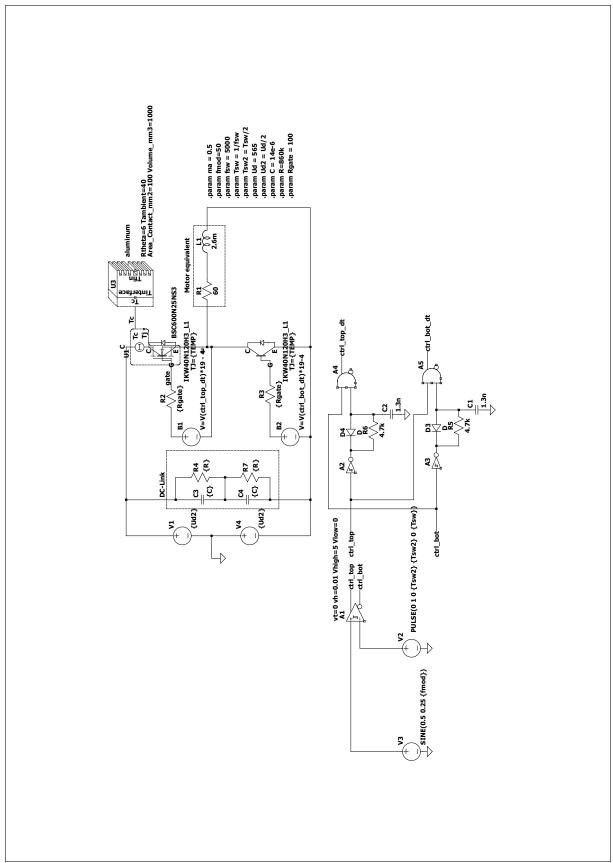

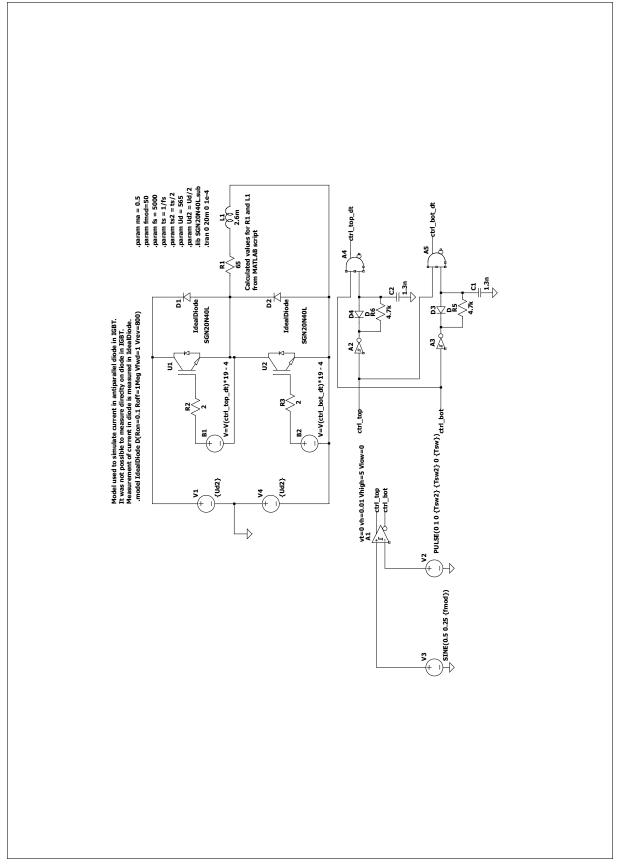

| D Simulation Results XXX                                                                                                                             | V           |

| D.1 Simulation Model without Heat Sink                                                                                                               | Ι           |

| D.2 Simulation Model with Heat Sink                                                                                                                  | Ι           |

| D.3 Diode Current Model                                                                                                                              |             |

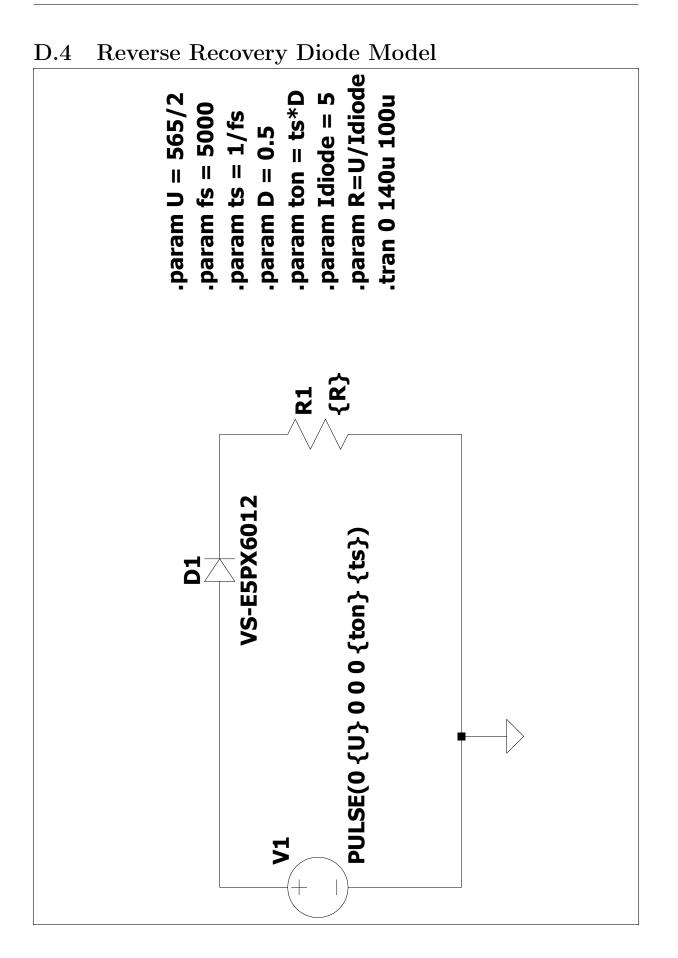

| D.4 Reverse Recovery Diode Model                                                                                                                     |             |

| D.5 Power Dissipation IGBT $(R_{gate} = 12 \Omega)$                                                                                                  |             |

| D.6 Power Dissipation IGBT $(R_{gate} = 50 \Omega)$                                                                                                  |             |

| D.7 Power Dissipation IGBT $(R_{gate} = 75 \Omega)$                                                                                                  |             |

| D.8 Power Dissipation IGBT $(R_{gate} = 100 \Omega)$ XLII                                                                                            |             |

| D.9 Thermal Calculations                                                                                                                             | V           |

| E Tools and Equipment XLV                                                                                                                            | Ι           |

| E.1 List of Software Tools                                                                                                                           | Ι           |

| E.2 List of Laboratory Equipment                                                                                                                     | Ι           |

| F Laboratory Exercise XLD                                                                                                                            | K           |

| Bibliography                                                                                                                                         | Ι           |

| Glossary                                                                                                                                             | Ι           |

| Acronyms                                                                                                                                             | Ι           |

## Figures

| 1                   | The circuitry to be fabricated                                                                                                         | 2                                      |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| $1.1 \\ 1.2$        | The equivalent circuit of an induction motor at standstill                                                                             | 7<br>8                                 |

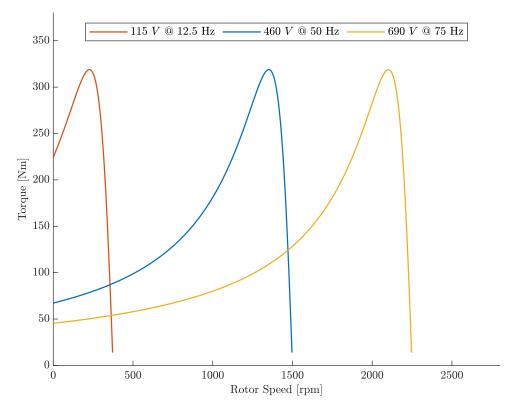

| 1.3                 | Torque-speed curve of an induction motor operated at different voltages with constant $U/f$ ratio.                                     | 9                                      |

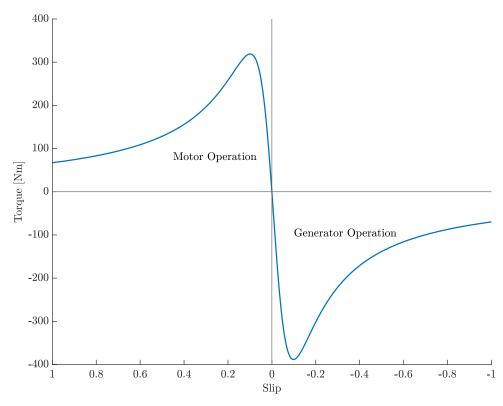

| 1.4                 | Torque-speed curve of an induction motor in motor and generator mode.                                                                  | 12                                     |

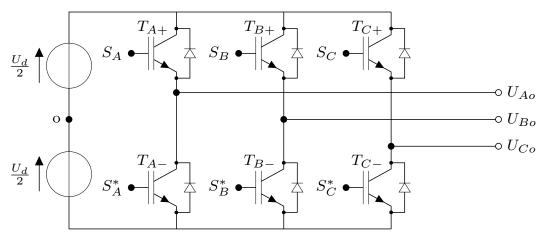

| $2.1 \\ 2.2 \\ 2.3$ | Three-phase two-level inverter topology                                                                                                | 16<br>18                               |

| 2.4                 | inverter                                                                                                                               | $\begin{array}{c} 20\\ 23 \end{array}$ |

| 2.5                 | Sinusoidal PWM in square wave operation.                                                                                               | 20<br>24                               |

| 2.6                 | Working principle of a two-level Space Vector PWM modulated inverter.                                                                  | 26                                     |

| 2.7                 | Basic voltage vector hexagon (zero vectors not shown)                                                                                  | 28                                     |

| 2.8                 | Average voltage space vector in sector 1 ( $\theta_s = 40^\circ$ )                                                                     | 29                                     |

| 2.9                 | Space Vector PWM in the overmodulating region                                                                                          | 33                                     |

| 4.1                 | Simplified circuit diagram.                                                                                                            | 43                                     |

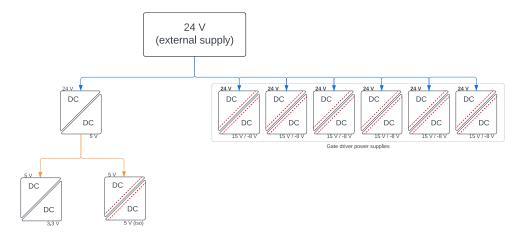

| 5.1                 | Power supply topology.                                                                                                                 | 45                                     |

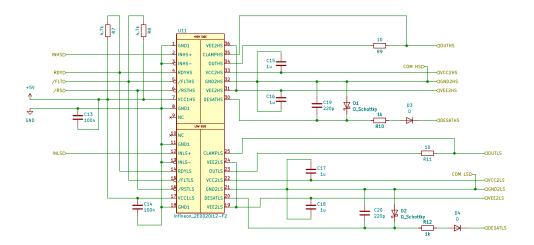

| 5.2                 | Gate driver topology.                                                                                                                  | 48                                     |

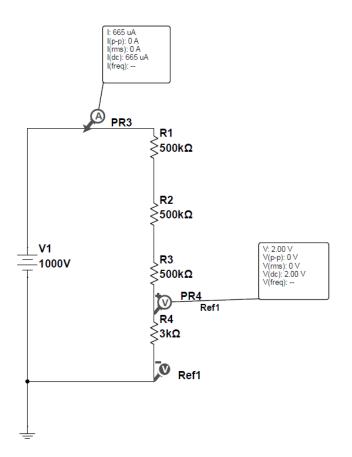

| 5.3                 | Voltage divider $(1000 \text{ V DC-source})$ .                                                                                         | 51                                     |

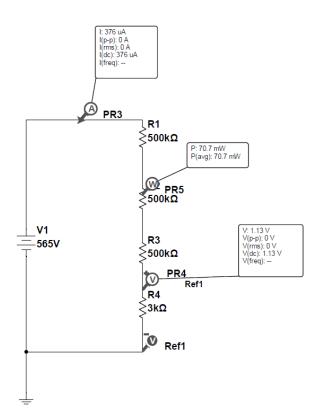

| 5.4<br>5 5          | Voltage divider (565 V DC-source).                                                                                                     | 53<br>E 4                              |

| $5.5 \\ 5.6$        | Differential operational amplifier                                                                                                     | $54 \\ 54$                             |

| 5.0<br>5.7          | Voltage measuring bridge with operational amplifier.                                                                                   | $55 \\ 55$                             |

| 5.8                 | Braking circuit topology.                                                                                                              | 56                                     |

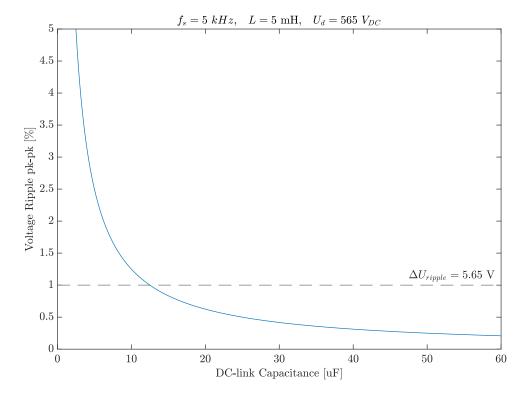

| 5.9                 | Voltage ripple as a function of DC-link capacitance.                                                                                   | 58                                     |

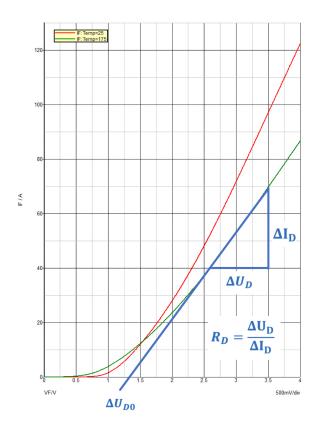

| 6.1                 | Typical diode forward current as a function of forward voltage                                                                         | 66                                     |

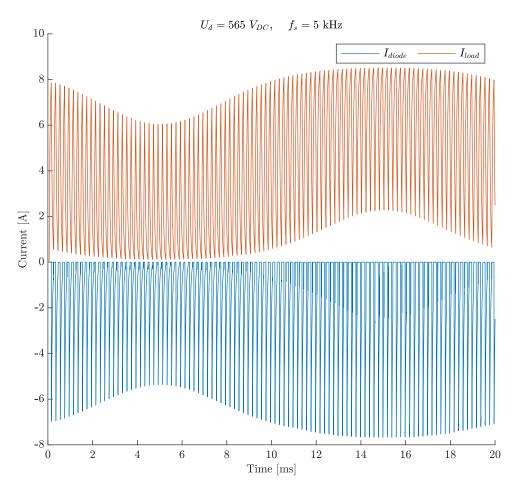

| 6.2                 | Diode current in nominal operation.                                                                                                    | 67                                     |

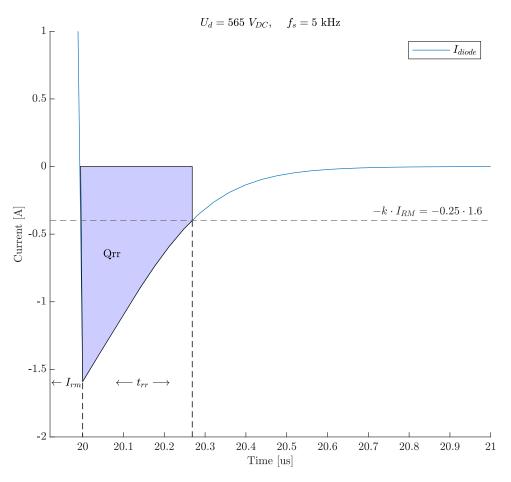

| 6.3                 | Reverse recovery current in diode                                                                                                      | 69                                     |

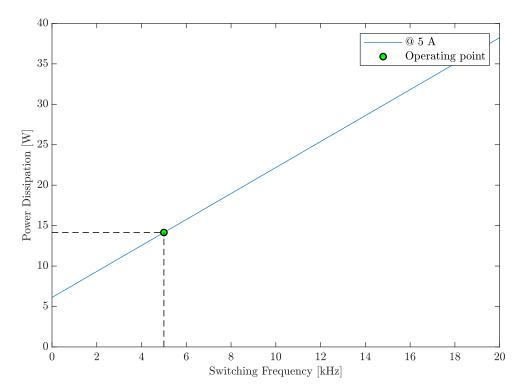

| 6.4                 | Power dissipation as function of switching frequency.                                                                                  | 71                                     |

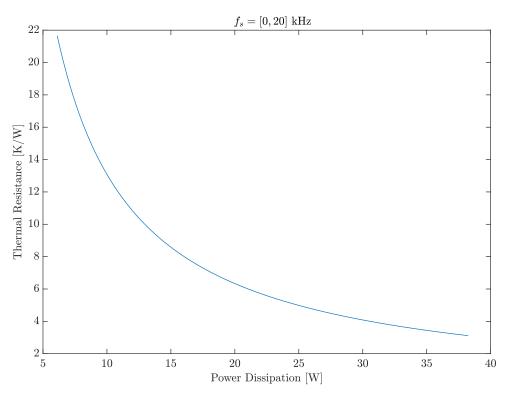

| 6.5                 | Thermal resistance as a function of power dissipation                                                                                  | 74                                     |

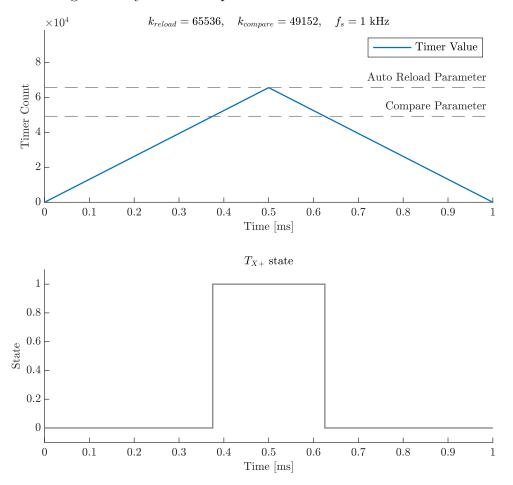

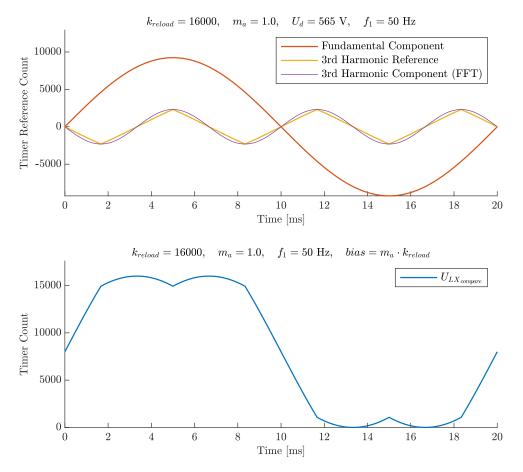

| $7.1 \\ 7.2$        | Working principle of the microcontroller's embedded PWM timers<br>Anticipated outcome through the generation of a Sinusoidal PWM modu- | 77                                     |

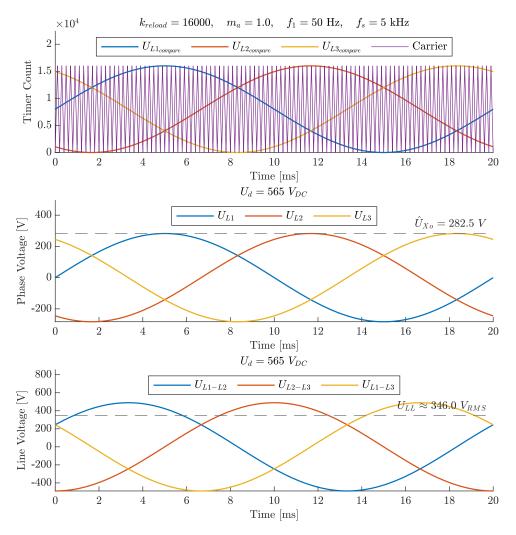

| . –                 | lated signal $(U_d = 565 \mathrm{V_{DC}})$ .                                                                                           | 81                                     |

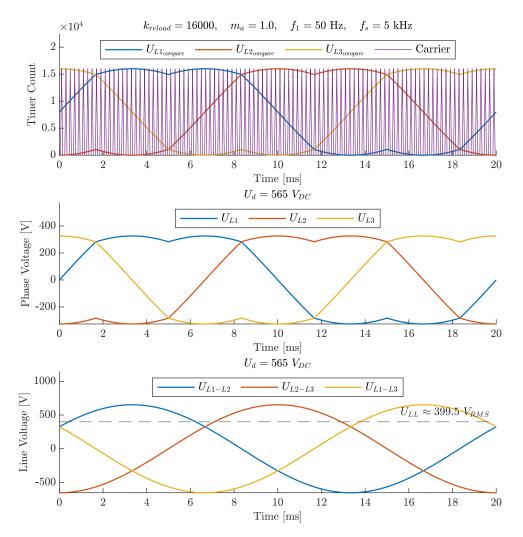

| 7.3<br>7.4   | Injection of third harmonic content utilizing the SV-PWM algorithm<br>Anticipated outcome through the generation of a Space Vector PWM modulated signal ( $U_d = 565 V_{DC}$ ).                             | 84<br>85 |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

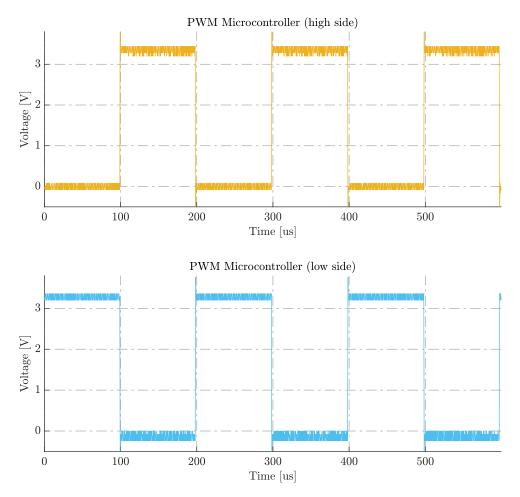

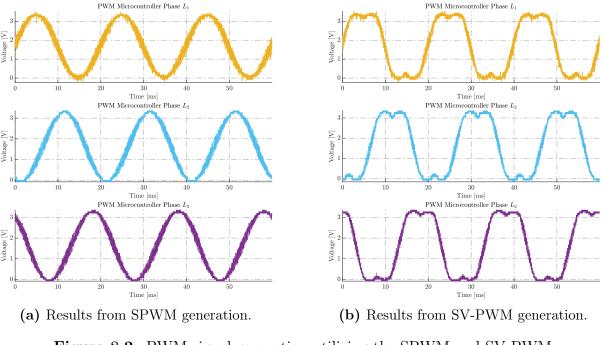

| $8.1 \\ 8.2$ | Validation of PWM signal generation $(D = 50\%, f_s = 5 \text{ kHz})$ PWM signal generation utilizing the SPWM and SV-PWM technique                                                                         | 88       |

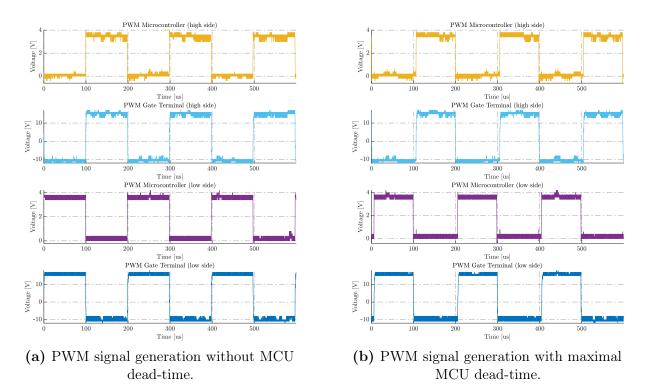

| 8.3          | $(m_a = 1.0, f_1 = 50 \text{ Hz}, f_s = 5 \text{ kHz}).$ Comparison of PWM signals with and without dead-time from the micro-                                                                               | 89       |

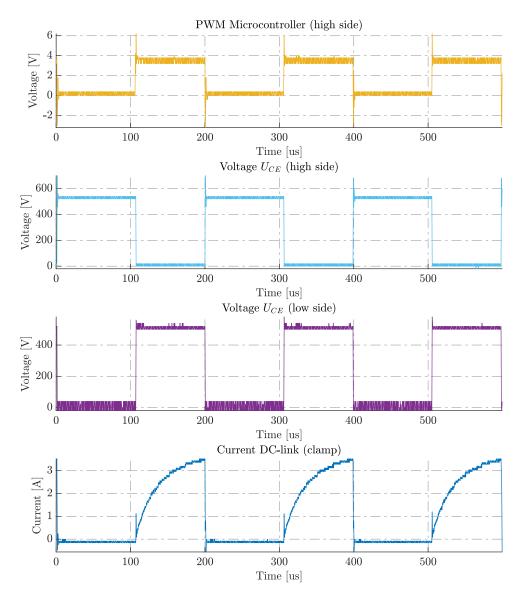

| 8.4          | controller $(D = 50\%, f_s = 5 \text{ kHz}, U_d = 0 \text{ V}_{\text{DC}}, R_{gate} = 100 \Omega)$ Switching behavior of the transistors $(D = 50\%, f_s = 5 \text{ kHz}, U_d = 500 \text{ V}_{\text{DC}})$ | 90       |

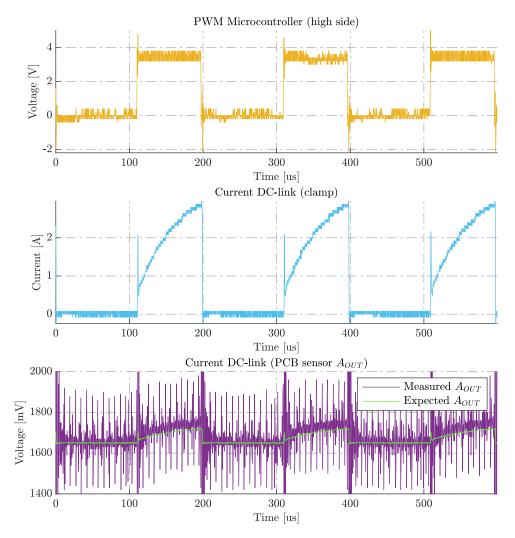

| 8.5          | $R_{gate} = 100 \Omega$ )                                                                                                                                                                                   | 91       |

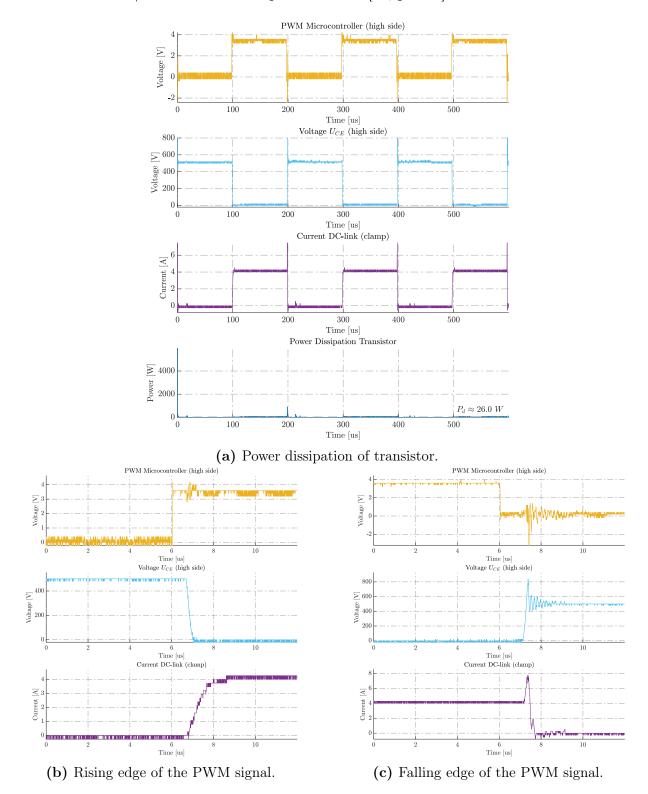

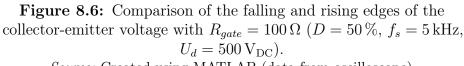

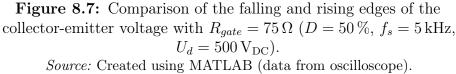

| 8.6          | $R_{gate} = 100 \Omega$ )                                                                                                                                                                                   | 92       |

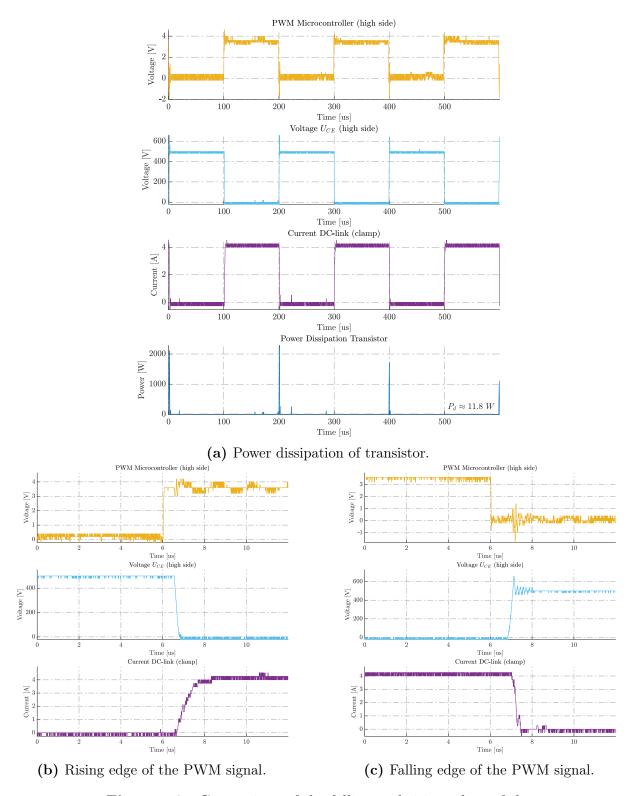

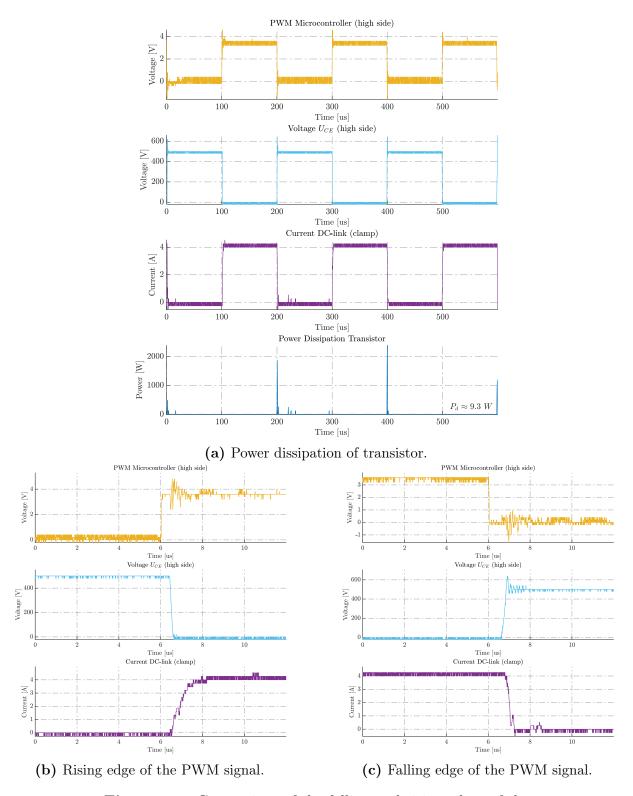

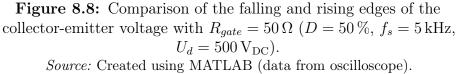

| 8.7          | with $R_{gate} = 100 \Omega$ ( $D = 50 \%$ , $f_s = 5 \text{ kHz}$ , $U_d = 500 \text{ V}_{\text{DC}}$ ) Comparison of the falling and rising edges of the collector-emitter voltage                        | 93       |

|              | with $R_{gate} = 75 \Omega \ (D = 50 \%, f_s = 5 \text{ kHz}, U_d = 500 \text{ V}_{\text{DC}}).$                                                                                                            | 94       |

| 8.8          | Comparison of the falling and rising edges of the collector-emitter voltage<br>with $R_{gate} = 50 \Omega$ ( $D = 50 \%$ , $f_s = 5 \text{ kHz}$ , $U_d = 500 \text{ V}_{\text{DC}}$ )                      | 95       |

| 8.9          | Comparison of the falling and rising edges of the collector-emitter voltage with $R_{gate} = 12 \Omega$ ( $D = 50 \%$ , $f_s = 5 \text{ kHz}$ , $U_d = 500 \text{ V}_{\text{DC}}$ )                         | 96       |

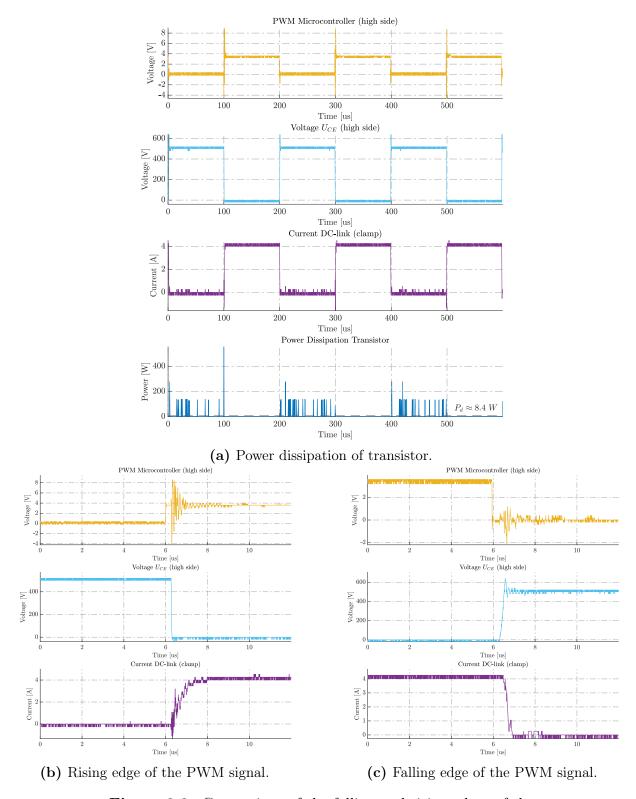

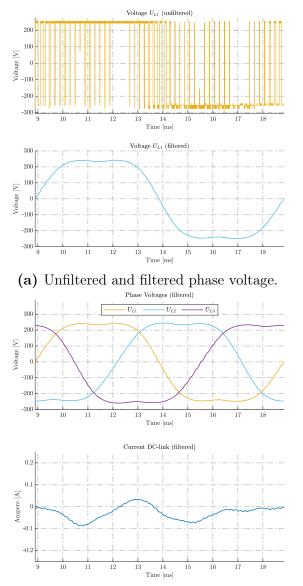

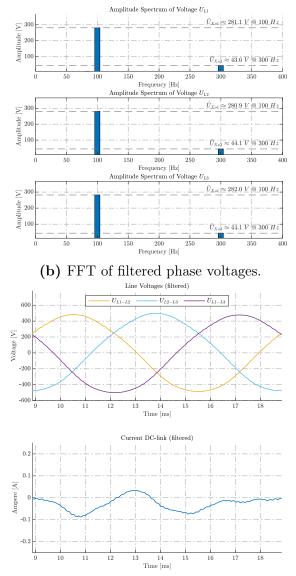

| 8.10         | Verified voltage outcome through the generation of a Sinusoidal PWM modulated signal ( $R_{gate} = 50 \Omega$ , $f_1 = 100 \text{ Hz}$ , $f_s = 5 \text{ kHz}$ , $U_d = 500 \text{ V}_{\text{DC}}$ ,        |          |

| 8.11         | $m_a = 1.0$ )                                                                                                                                                                                               | 98       |

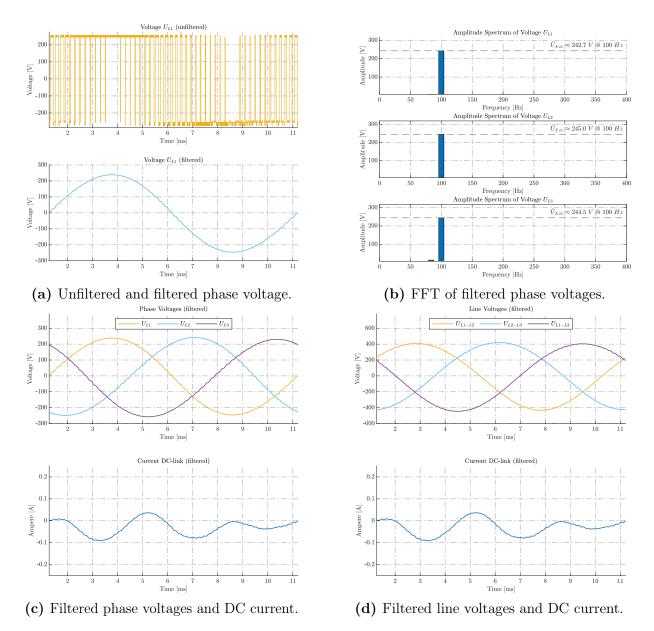

|              | 50% reduction in the $U/f$ ratio ( $R_{gate} = 50 \Omega$ , $f_1 = 50 \text{ Hz}$ , $f_s = 5 \text{ kHz}$ , $U_d = 500 \text{ V}_{\text{DC}}$ , $m_a = 0.5$ )                                               | 99       |

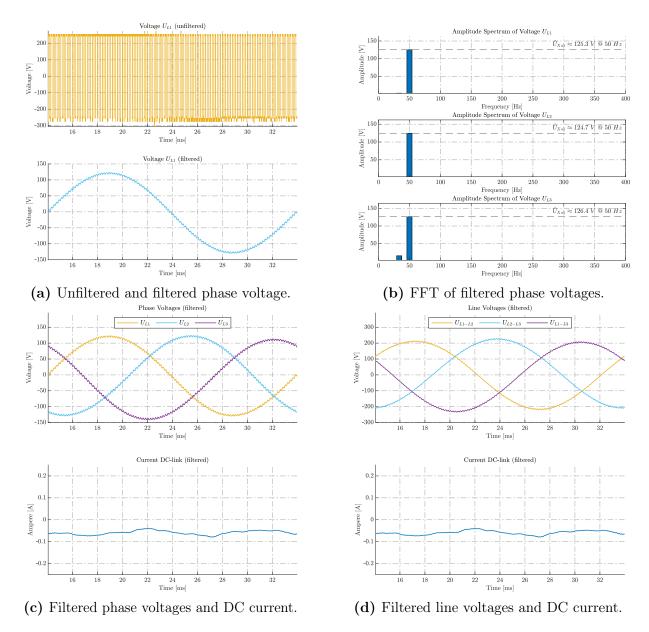

| 8.12         | Verified voltage outcome through the generation of a Space Vector PWM modulated signal ( $R_{gate} = 50 \Omega$ , $f_1 = 100 \text{ Hz}$ , $f_s = 5 \text{ kHz}$ , $U_d = 500 \text{ V}_{\text{DC}}$ ,      |          |

| 8.13         | $m_a = 1.0$ )                                                                                                                                                                                               | 100      |

|              | 50% reduction in the $U/f$ ratio ( $R_{gate} = 50 \Omega$ , $f_1 = 50 \text{ Hz}$ , $f_s = 5 \text{ kHz}$ , $U_d = 500 \text{ V}_{\text{DC}}$ , $m_a = 0.5$ )                                               | 101      |

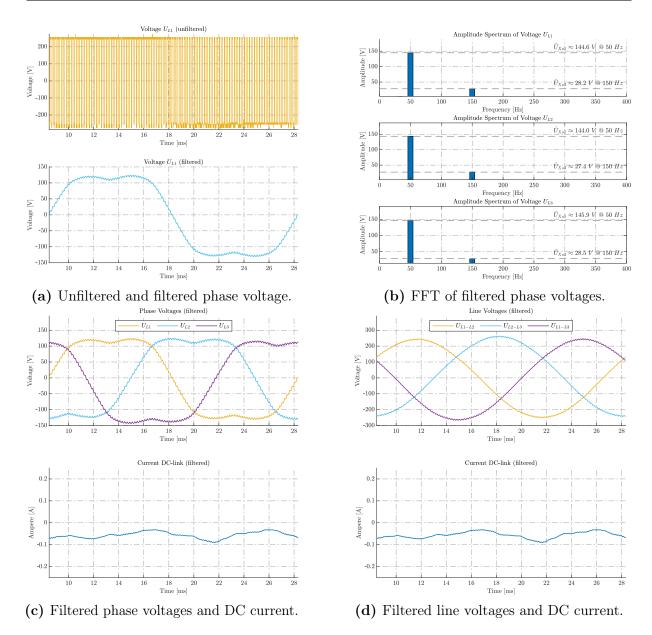

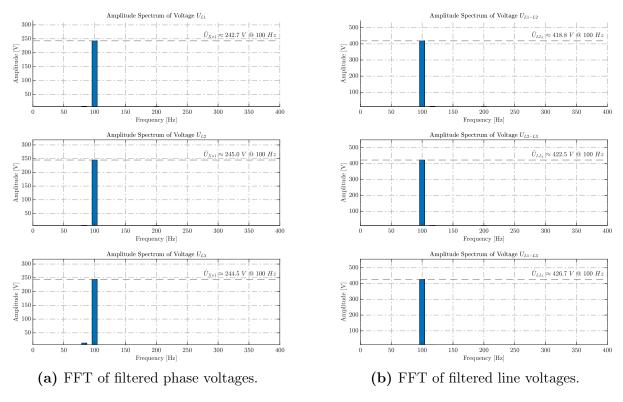

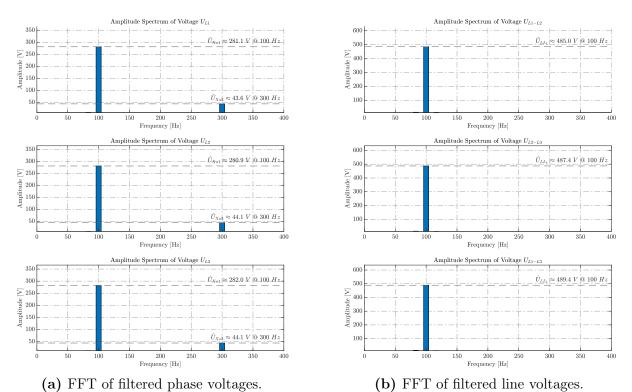

| 9.1          | Fast Fourier Transform of SPWM generated voltages (data from the experi-<br>ments conducted in Figure 8.10).                                                                                                | 109      |

| 9.2          | Fast Fourier Transform of SV-PWM generated voltages (data from the experiments conducted in Figure 8.12)                                                                                                    | 110      |

## Tables

| $2.1 \\ 2.2 \\ 2.3$ | Zero and basic voltage vectors for a two-level inverter                                                                                                | 27<br>30<br>30 |

|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| 3.1                 | Electrical specifications for the inverter                                                                                                             | 36             |

| 5.1                 | Available voltage levels on the PCB                                                                                                                    | 46             |

| 9.1                 | Theoretical calculations versus oscilloscope readings $(U_d = 500 \text{ V}_{\text{DC}}, m_a = 1.0, f_1 = 100 \text{ Hz})$ .                           | 107            |

| B.1                 | List of components employed in a single inverter                                                                                                       | KVI            |

|                     | List of software tools that has been used throughout the project XI<br>List of laboratory equipment utilized during the testing phase of the design.XL |                |

## Code Listings

| B.1 | Script for calculation of DC-link capacitors (MATLAB).      | XXX    |

|-----|-------------------------------------------------------------|--------|

| C.1 | Microcontroller code for the Sinusoidal PWM algorithm (C)   | XXXII  |

| C.2 | Microcontroller code for the Space Vector PWM algorithm (C) | XXXIII |

| D.1 | Script for thermal calculations (MATLAB).                   | XLIV   |

## Introduction

According to global energy consumption statistics, nearly two-thirds of the energy used worldwide is consumed by motor drives [7, p. xi], with induction motors accounting for 80 % of the energy [17]. Induction motors, also referred to as asynchronous motors, are highly efficient electrical machines that convert electrical energy into mechanical energy. Their reliability and simple construction have made them the most commonly used electric motor in the world, being employed in a wide range of applications, from household appliances to industrial systems. In recent years, the induction motor has also gained significant market share in mobile applications, such as electric vehicles [7, p. 3-4].

### Background

The induction motor comprises a stationary part known as the stator and a rotating part known as the rotor. Its operation relies on the principle of electromagnetic induction, which states that a magnetic field can induce an electrical current in a nearby conductor. In the case of induction motors, such a magnetic field is generated by passing an alternating current (AC) through the stator windings. This induces a current in the rotor windings, causing the rotor shaft to rotate [7, p. 194-199]. To achieve optimal efficiency, precise control of the rotor speed and torque is essential. The amplitude and frequency of the stator voltage are the primary determinants of these parameters and can be adjusted using a Power Processing Unit (PPU).

A common approach to power processing involves rectifying the alternating power supply into direct current (DC) and subsequently utilizing modulation techniques, such as Pulse Width Modulation (PWM), to reconvert it to AC waveforms with the appropriate voltage and frequency. An electronic device known as an inverter is central in enabling this conversion, working by switching the DC voltage on and off at high frequencies to generate sinusoidal waveforms with the desired characteristics.

### **Project Overview**

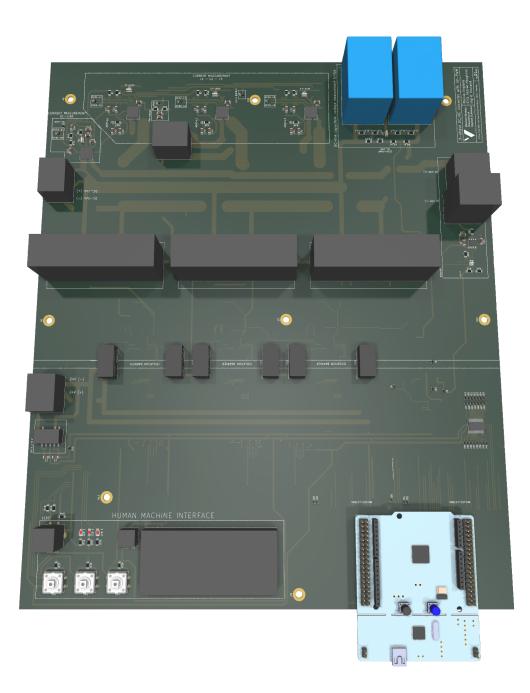

The aim of this project is to design and fabricate a two-level inverter that utilizes the Space Vector Pulse Width Modulation (SV-PWM) algorithm to generate a three-phase alternating current from a direct current source, thereby enabling the control of induction motors. The finalized circuit design, together with its associated research, will serve as a learning resource in future laboratory exercises at Western Norway University of Applied Sciences.

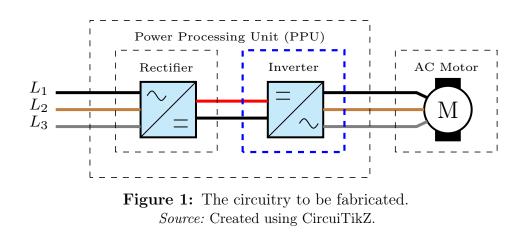

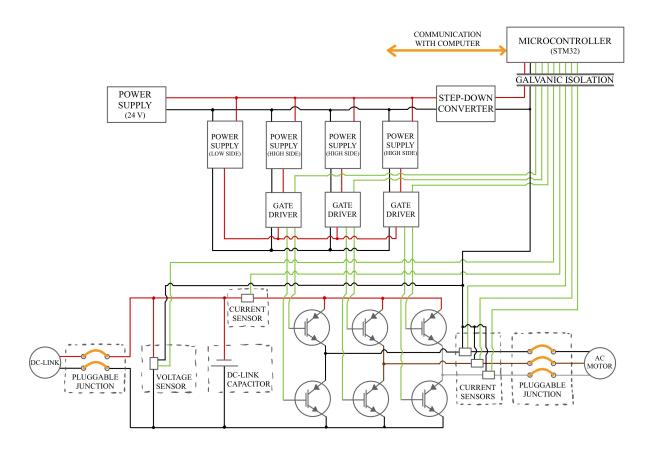

In Figure 1, the delineated section highlighted by the blue dashed line represents the specific circuitry to be fabricated within the context of a Power Processing Unit.

### Employer

Western Norway University of Applied Sciences, also known as HVL, is a highly esteemed institution of higher education located in Norway and serves as the commissioning body for the present project. As one of the largest universities in the country, HVL covers a total of 17 000 students and 1750 staffs. The university is comprised of four faculties, each of which offers a diverse range of undergraduate and graduate programs. The faculties span the fields of health and social sciences, education, culture and sports, engineering and natural sciences, economics and social sciences. Annually HVL graduates approximately 4500 candidates [10].

### Structure of the Report

This chapter has introduced the induction machine and the inverter, along with a presentation of the project's objective and employer. Moving forward, the report is divided into three parts, each focusing on a specific aspect of the project.

The initial part explores the induction machine, including various control methodologies and the challenges associated with inverter design. Moreover, it delves into the theoretical principles of different modulation techniques and the respective strengths and limitations of each. This section establishes the fundamental basis for the subsequent design development.

The second part is dedicated to the design process, which begins with an assessment of the demands and specifications that must be incorporated into the design. Following this, a comprehensive exposition of the design process is provided, with due consideration given to various design factors that are critical for achieving the desired outcomes.

The third part is primarily focused on practical verification of the design through laboratory experiments. It presents an overview of the methodology used in these experiments, along with an analysis of the results.

In conclusion, the report summarizes the three parts and evaluates the finalized design. The report also suggests areas for **further improvement** in future work.

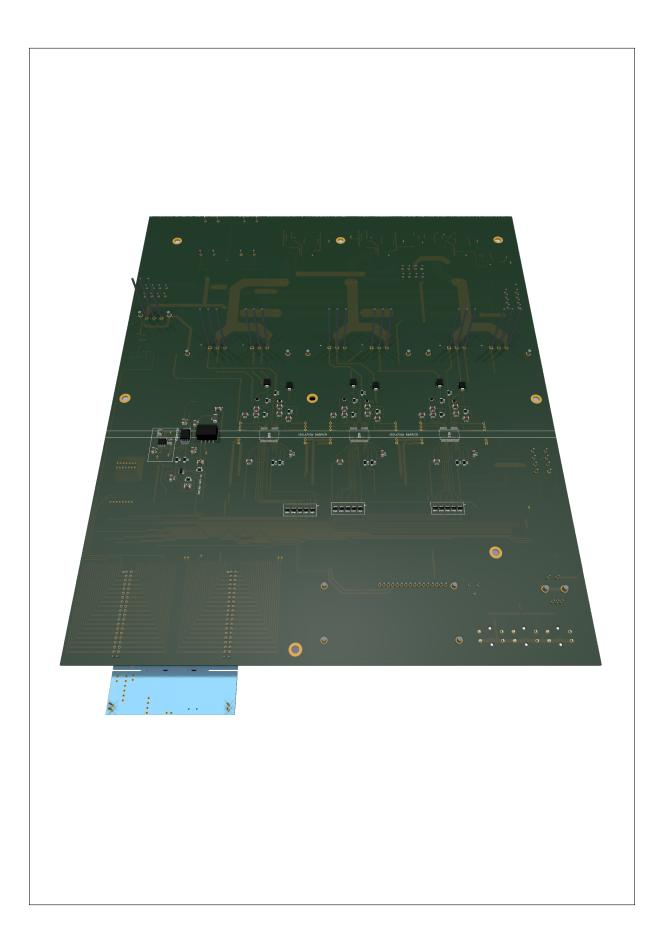

Additionally, **the appendices** comprise of supplementary details on project management and helpful resources for potential future contributions. These encompass a range of materials, including 3D models, PCB layout, circuit diagrams, identified design flaws, program code, simulation results and a laboratory exercise for educational purposes.

## Part I

## Theory

## Chapter 1

## **Induction Machines and Operation**

As asserted in the introductory chapter, the induction machine holds a prominent position as the most widely used electric motor worldwide. This popularity stems from the machine's ability to maintain a nearly constant speed under constant voltage and frequency [7, p. 193]. Nevertheless, to effectively regulate the speed and torque, it is imperative to grasp the operational principles of the machine. The three-phase induction machine is built upon a simple structure of three stator windings that are mutually displaced in space by 120 degrees. Upon supplying these windings with current, a magnetic field is generated and utilized in the rotor to rotate a shaft, which is usually connected to a mechanical load. This chapter aims to introduce the construction of the machine, elucidate some methods of controlling its speed and torque, and also examines the underlying principles governing its operation as a generator, which is crucial in inverter design.

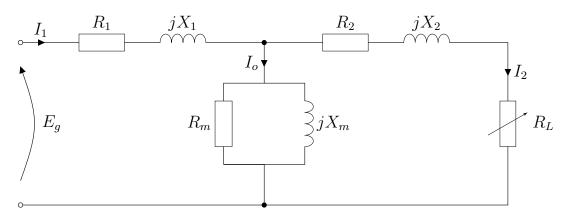

### 1.1 Electrical Model

It is essential to examine the equivalent circuit depicted in Figure 1.1 to gain a thorough understanding of the induction motor. Through the use of the equivalent circuit, which is based on a wye connection for the stator and rotor, each winding can be visualized for each phase. Such a comprehensive overview provides insight into the multifarious parameters that influence the motor [4, p. 330].

Figure 1.1: The equivalent circuit of an induction motor at standstill. Source: Created using CircuiTikZ.

The left-hand side of the equivalent circuit visualizes the phase voltage,  $E_g$ , that is connected to the stator windings. The stator comprises a winding resistance,  $R_1$ , and a leakage reactance,  $jX_1$ , while the current flowing through them represents the line current,  $I_1$ . These parameters are important for modeling the behavior of the induction machine under different operating conditions, such as varying loads or frequency [4, p. 273].

In the middle of the equivalent circuit, the magnetizing resistance,  $R_m$ , and magnetizing reactance,  $jX_m$ , form a magnetizing branch with the corresponding magnetizing current,  $I_o$ . The electrical losses in  $R_m$  corresponds directly to iron, windage and friction losses in the motor, while the value of  $jX_m$  affects the reactive power generated by the motor.

On the right-hand side, the rotor is illustrated, comprising a winding resistance,  $R_2$ , and a leakage reactance,  $jX_2$ . These parameters are important in determining the motor's starting and running performance, as well as its efficiency [4, p. 264].

The output is illustrated with a variable resistive load,  $R_L$ , allowing the regulation of the motor's load current,  $I_2$ . This change in current can affect the torque produced by the motor, which in turn can impact its speed and efficiency. The effective connection between one slip-ring and the neutral of the rotor is established through the presence of  $R_L$  [4, p. 331-332].

### 1.2 Speed and Torque Control

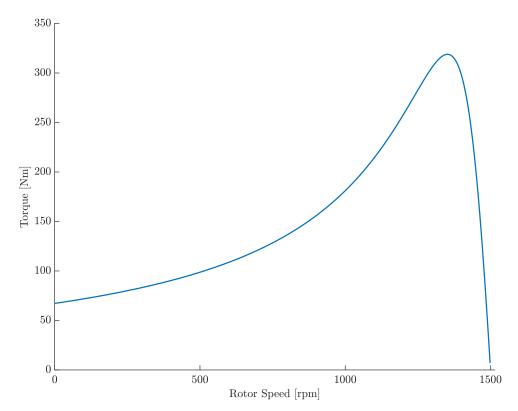

One of the most significant benefits of Variable Frequency Drive (VFD) is their ability to achieve the same level of torque without any increase in current. This is due to the VFD's ability to adjust the frequency of the voltage supplied to the motor, which in turn controls the speed of the motor. By adjusting the frequency of the voltage, VFD's can vary the amount of power supplied to the motor, allowing the motor to operate at the desired speed and torque with minimal energy consumption [4, p. 471-474]. The relationship between speed and torque developed in a motor is often visualized using a torque-speed curve as demonstrated in Figure 1.2.

Figure 1.2: Typical torque-speed curve of an induction motor operated at fixed voltage and frequency. Source: Created using MATLAB.

#### Constant U/f

Scalar control, also known as constant U/f, is a commonly used method to control the speed and torque in variable frequency drives. The method involves a modulator for proportionally varying the amplitude and frequency of the voltage applied to the stator windings, which enables the motor to deliver maximum rated torque while keeping frequency, rotor current, and stator current within rated values. However, varying mechanical loads may affect the accuracy of the output due to motor slip. When the operating frequency of the motor falls below approximately 20% of its rated frequency,  $f_n$ , it becomes necessary to progressively increase the volts-per-hertz ratio to offset the voltage drop resulting from the resistance of the stator windings [4, p. 472]. Scalar control is recognized as a technically uncomplicated and cost-effective approach to motor control in contrast to alternative VFD methods.

Figure 1.3: Torque-speed curve of an induction motor operated at different voltages with constant U/f ratio. Source: Created using MATLAB.

The characteristic curve depicted in Figure 1.2 exhibits consistent shape regardless of variations in frequency and voltage that occur in direct proportion. However, the key

distinction lies in the point at which it attains maximum torque, as illustrated in Figure 1.3. This indicates that the curve maintains its overall shape under U/f, but undergoes horizontal displacement as the frequency changes [4, p. 472].

#### Direct Torque Control

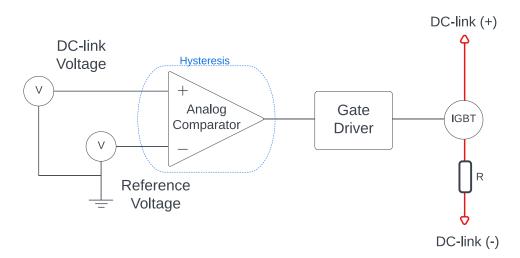

Direct Torque Control (DTC) is a more advanced motor control technique that estimates motor torque based on current and voltage measurements. It employs a precise and efficient mathematical algorithm to achieve direct control of the motor's torque. This approach requires only basic motor parameters and measurements, and eliminates the need for a modulator [9, no. 1, p. 16]. However, due to the rapid fluctuations in current resulting from the calculation of the inverter's control signals, this method may introduce noise-related issues. Torque and flux are restricted to specific upper and lower limits, with smaller limits resulting in higher accuracy. By minimizing the discrepancy between desired and estimated torque, DTC maximizes the effectiveness of torque control. This method, also known as hysteresis control, exploits the characteristic phenomenon of hysteresis to improve torque control accuracy [4, p. 644].

DTC's torque response is approximately ten times better than most alternating current (AC) or direct current (DC) drives, making the motor more reliable even in the presence of a rapidly changing mechanical load [9, no. 1, p. 14]. Unlike Pulse Width Modulation (PWM), which typically relies on a constant switching frequency, DTC employs a switching frequency that is determined by the change in torque and stator flux of the motor. This dynamic nature of switching frequency ensures the control of torque and flux to be highly responsive and precise [4, p. 556].

#### Field Oriented Control

Field Oriented Control (FOC), also known as flux vector control, is a more complicated technique used to regulate the speed and torque of a motor. The method accomplishes its objective by effectively aligning the magnetic fields of the stator and rotor in an orthogonal manner, thereby maximizing the motor's torque output. Compared to other motor control methods such as scalar control, FOC uses more advanced control algorithms and digital signal processing techniques to calculate the optimal current required to produce the desired magnetic field and torque. This current is then fed to the motor's stator windings using power electronics such as inverters, which enables accurate regulation of the motor's speed and torque, even in situations of varying load conditions. It has been shown that this significantly improve the motor's efficiency and performance compared to conventional control techniques [4, p. 630-632].

### 1.3 Generator Mode Operation

Regenerative operation, also known as regenerative braking, is a feature that allows an induction motor to operate as a generator. In many wind-electric systems, induction motors are utilized to convert wind energy into electrical energy, which can be transmitted to the power grid. In such applications, the power flow within the system is unidirectional. Induction motors always operate at an asynchronous speed relative to the magnetic field in the rotor. The difference between the speed of the motor's shaft and the rotational speed of the magnetic field is referred to as slip speed. Furthermore, Equation 1.1 depicts how the frequency, f, of the voltage and the number of pole pairs, p, affect the motor's synchronous speed,  $n_1$  [9, no. 7, p. 11].

$$n_1 = \frac{f \cdot 60}{p} \tag{1.1}$$

The induction motor operates with positive slip, denoted s, when the speed of the magnetic field in the stator is greater than the shaft's rotational speed. This can be expressed in percent using Equation 1.2, where the rotor speed,  $n_2$ , varies with the mechanical load of the motor. In contrast, the synchronous speed of the rotor remains constant as long as the frequency of the applied voltage is constant. Power flows from the electrical grid to the motor in this mode of operation.

$$s = \frac{n_1 - n_2}{n_1} \cdot 100\% \tag{1.2}$$

Considering an electrical train travelling downhill with induction motors directly connected to its wheels, the motors rotates above synchronous speed due to gravitational forces. As the motors rotate above synchronous speed a counter torque, that opposes the increase in speed, is developed, acting as a brake. However, the braking energy returns as electrical energy via the motor's three phase connection [4, p. 319-320]. Figure 1.4 illustrates the transition from motor to generator, with the intersection of the curve through the y-axis defining the transition point, where the slip is equal to 0.

Figure 1.4: Torque-speed curve of an induction motor in motor and generator mode. Source: Created using MATLAB.

In variable speed drives, the rectifier is usually a 6-pulse or 12-pulse diode rectifier delivering power from the AC grid to the inverter's DC-link. The rectifier can only deliver power unidirectional, allowing power to flow exclusively from the AC grid to the DC-link. If a motor connected to a frequency inverter transitions to regenerative operation, the motor delivers power that charges the DC-link capacitors as shown in Equation 1.3 and 1.4 [9,

no. 2, p. 13].

$$W = P \cdot t = \frac{C \cdot U_{DC}^2}{2} \tag{1.3}$$

$$U_{DC} = \sqrt{\frac{2 \cdot W}{C}} \to \sqrt{\frac{2 \cdot P \cdot t}{C}}$$

(1.4)

Charging of the DC-link capacitors can lead to high voltages that can cause serious damage to the capacitors and the inverter. To prevent excessive voltage increase, there are four primary alternatives available: overvoltage control, braking chopper, Active Front End (AFE), or common DC configuration.

The initial approach entails controlling the power returned from the motor by constraining the braking torque to uphold a consistent DC-link voltage. This method is called overvoltage control, and is a standard feature in most new drives.

The second option for limiting the DC-link voltage is directing the braking energy to a resistor through a braking chopper. The braking chopper is a switch that connects the DC-link to a resistor where the braking energy is dissipated and converted into heat. The braking function is automatically activated when the DC-link voltage exceeds a set limit. This method is a simple circuit design and is inexpensive to implement. A significant disadvantage is that the dissipated energy becomes futile if the heated air cannot be harnessed for any useful purpose.

The third alternative involves employing an inverter with Active Front End capability. This type of inverter incorporates a controlled rectifier, enabling its operation in all four quadrants. Having a bi-directional rectifier allows bi-directional power flow between the AC and DC side of the inverter. This solution is desirable if the motor system generates large braking energy that could be fed back to the AC grid.

In scenarios where a system involves multiple drives, it is possible for one motor to operate in regenerative mode while others continue to function as motors. Consequently, the implementation of a common DC system presents itself as the final option. This system employs an inverter design that effectively reuses the mechanical energy generated during braking, promoting energy efficiency and resource utilization. The system consists of separate rectifiers and inverters feeding the AC motors, where the common DC bus is the key for moving the braking energy from one motor to benefit the other motors in the system [9, no. 3, p. 15-25].

### Chapter 2

## Power Conversion with PWM

As previously mentioned, Power Processing Units (PPUs) are integral in adapting the electrical voltage and frequency of the utility line<sup>1</sup>, thus enabling the regulation of the rotor speed and torque of the induction machine. As shown in Figure 1, PPUs are composed of two primary constituents. The rectifying section, also known as a rectifier, converts alternating current to direct current, establishing a DC-link. The alternating section, referred to as an inverter, utilizes Pulse Width Modulation (PWM) on the DC-link to generate a sinusoidal voltage. This chapter provides an introduction to inverters and examines some various modulation techniques that can be employed to regulate the induction machine.

### 2.1 Three-Phase Two-Level Inverters

Inverters are primarily utilized to convert DC to AC, which is useful in mobile applications where only DC power is available. However, due to the underlying technique, inverters are also employed in situations where AC power is already accessible. Figure 2.1 illustrates a three-phase two-level inverter composed of a DC-link and six transistors, two of which form a leg. The transistors operate in pairs as switches that alter the polarity of the

<sup>&</sup>lt;sup>1</sup> A utility line in electricity refers to the system of wires and equipment that are used to transmit and distribute electrical power from a power plant or substation to customers [13].

voltages  $U_{Ao}$ ,  $U_{Bo}$ , and  $U_{Co}$ . By turning the transistors on and off in a specific pattern with high frequency, an AC voltage can be replicated. This is adjustable in terms of amplitude and frequency, subject only to constraints imposed by the DC-link and the modulation algorithm utilized.

Figure 2.1: Three-phase two-level inverter topology. *Source:* Created using CircuiTikZ.

The use of Pulse Width Modulation is ubiquitous in the operation of inverters across various applications. Irrespective of the specific application, the fundamental principle behind PWM remains constant. In essence, the technique involves generating variable-width pulses to mimic the amplitude of an analog input signal. The modulated signal produced in this manner can accurately replicate the desired AC voltage waveform. Although diverse PWM algorithms exist, the underlying principle remains predominantly the same.

#### Duty Cycle

Pulse Width Modulation entails modulating a square wave signal that alternates between two voltage levels,  $U_{max}$  and  $U_{min}$ , at high frequencies over a period  $T_s$ . The duration of the signal at the high and low levels, referred to as on-time,  $T_{on}$ , and off-time,  $T_{off}$ , respectively, is determined by a parameter known as the duty cycle, denoted by D, as expressed in Equation 2.1 [3, p. 162].

$$D = \frac{T_{on}}{T_{on} + T_{off}}$$

$$= \frac{T_{on}}{T_s}$$

(2.1)

The duty cycle represents the proportion of the signal's period during which it remains in the high state. Mathematically, the relationship between the duty cycle and the average voltage,  $\overline{U}$ , can be represented as demonstrated in Equation 2.2.

$$\overline{U} = \frac{1}{T_s} \left( \int_0^{D \cdot T_s} U_{max} dt + \int_{D \cdot T_s}^{T_s} U_{min} dt \right)$$

$$= \frac{1}{T_s} \left( D \cdot T_s \cdot U_{max} + (1 - D) \cdot T_s \cdot U_{min} \right)$$

$$= D \cdot U_{max} + (1 - D) \cdot U_{min}$$

(2.2)

In the context of inverters, PWM is applied to a DC-link, wherein the voltage have linearity with a nearly steady value. As a result,  $U_{min}$  is not applicable, allowing for a further simplification of Equation 2.2:

$$\overline{U} = D \cdot U_{max} \tag{2.3}$$

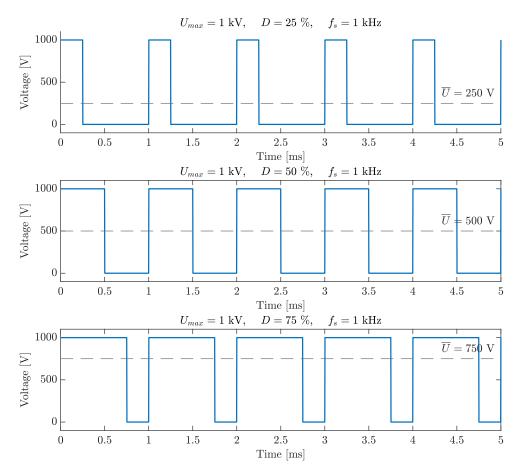

Figure 2.2 illustrates the correlation between duty cycle and average output voltage, where various duty cycles are represented in relation to a DC-link voltage of 1000 V. The figure consists of five time periods at a switching frequency of 1 kHz, which is introduced in the subsection that follows.

Figure 2.2: Relationship between PWM parameters. Source: Created using MATLAB.

#### Switching Frequency

The switching frequency,  $f_s$ , refers to the number of times the signal oscillates between the on and off states within the time period  $T_s$  [7, p. 48]. This correlation can be expressed using Equation 2.4.

$$f_s = \frac{1}{T_s} \tag{2.4}$$

A higher switching frequency yields greater precision in the generated voltage, however, it is accompanied by increased power losses in practical semiconductor applications. It should also be noted that the switching frequency exerts no influence on the averaged output voltage.

### 2.2 Sinusoidal Pulse Width Modulation

Sinusoidal Pulse Width Modulation (SPWM) is a widely used modulation technique that generates a sinusoidal voltage waveform through the manipulation of a carrier signal's frequency. When reasonable configured, it is a straightforward and efficacious approach, yielding minimal harmonic distortion. Nevertheless, it has the drawback of not fully utilizating the available DC-link voltage.

#### Working Principle

The operation of Sinusoidal Pulse Width Modulation involves the comparison between a sinusoidal waveform, denoted as the control signal,  $U_{control}$ , and a triangular waveform, referred to as the carrier signal,  $U_{tri}$ . The frequency of the sinusoidal waveform,  $f_1$ , determines the frequency of the output voltage, while the frequency of the triangular waveform determines the switching frequency,  $f_s$ , and implies the number of times the transistors change state within a period  $T_s$  [3, p. 203].

In an inverter design, the switches  $T_{X+}$  and  $T_{X-}$  are controlled by comparing the control signal with the carrier signal, resulting in an output voltage,  $U_{Xo}$ , that is half the voltage of the DC-link, either positive or negative [3, p. 204]:

$$U_{control} > U_{tri}, \qquad T_{X+} \text{ is on,} \qquad U_{Xo} = \frac{U_d}{2}$$

$$(2.5a)$$

$$U_{control} < U_{tri}, \qquad T_{X-} \text{ is on,} \qquad U_{Xo} = \frac{-U_d}{2}$$

(2.5b)

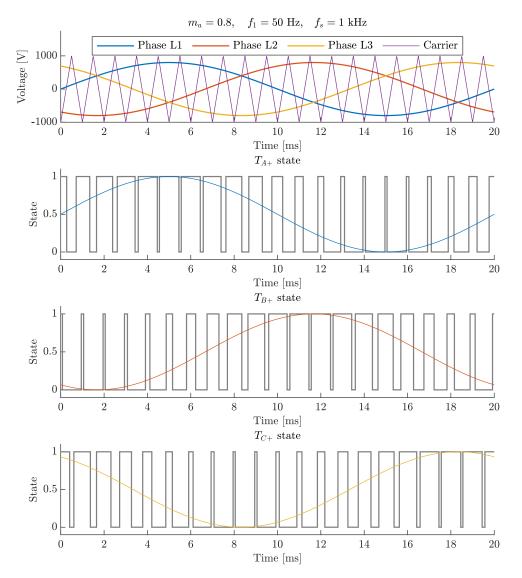

A comparison of three such control signals and the carrier signal governs the state of the switches at each leg, as shown in Figure 2.3. The conjugation between these prevents the occurrence of a scenario where both switches are in the same state, thus avoiding any possibility of a short circuit in the DC-link.

Figure 2.3: Working principle of a three-phased two-level Sinusoidal PWM modulated inverter. Source: Created using MATLAB.

### Linear Modulation

The interplay between the amplitudes of the control signal,  $\hat{U}_{control}$ , and the carrier signal,  $\hat{U}_{tri}$ , gives rise to a novel concept known as the amplitude modulation index,  $m_a$ , as explicated in Equation 2.6.

$$m_a = \frac{\hat{U}_{control}}{\hat{U}_{tri}} \tag{2.6}$$

Since the maximum value of the carrier signal remains largely constant, the amplitude modulation index is affected only by changing the control signal. An increased amplitude modulation index implies a stronger modulation of the carrier signal's amplitude, which leads to a broader spectrum of output voltages. However, this amplifies the distortion in the output voltage and can have a negative impact on the overall performance.

Assuming a carrier signal with an amplitude greater than or equal to the instantaneous value of the control signal, the average voltage,  $U_{Xo}$ , over a switching period can be expressed as the ratio between the two signals and the available DC-link voltage [3, p. 205], as shown in Equation 2.7.

$$U_{Xo} = \frac{U_{control}}{\hat{U}_{tri}} \cdot \frac{U_d}{2}, \qquad U_{control} \le \hat{U}_{tri}$$

(2.7)

Thus, the resultant instantaneous phase voltage of the fundamental frequency component,  $U_{Xo1}$ , can be sinusoidally expressed using Equation 2.8, while its peak voltage,  $\hat{U}_{Xo1}$ , can be derived from Equation 2.9 [3, p. 206].

$$U_{Xo1} = \frac{\hat{U}_{control}}{\hat{U}_{tri}} \cdot \frac{U_d}{2} \cdot \sin(\omega_1 \cdot t), \qquad \hat{U}_{tri} \ge \hat{U}_{control}$$

$$= m_a \cdot \frac{U_d}{2} \cdot \sin(\omega_1 \cdot t), \qquad m_a \le 1.0$$

(2.8)

$$\hat{U}_{Xo1} = m_a \cdot \frac{U_d}{2}, \qquad m_a \le 1.0$$

(2.9)

The aforementioned expressions assert that the output RMS line voltage,  $U_{LL_{RMS}}$ , within the linear region is ascertainable as  $\sqrt{3}/\sqrt{2}$  of the phase voltage,  $\hat{U}_{Xo1}$ , as evinced subsequently in Equation 2.16 within Section 2.3 explicating the Space Vector Pulse Width Modulation technique.

### Overmodulation

As explicitly expressed by Equation 2.9, the output voltage exhibits a linear variation with respect to the amplitude modulation index as long as it remains below 1.0. However, if the amplitude of the control signal surpasses that of the carrier signal ( $m_a > 1.0$ ), the inverter enters a region known as the overmodulating region [3, p. 208]. Within this region, the output voltage will contain a larger number of harmonics compared to linear modulation, and it will no longer vary linearly with the amplitude modulation index [3, p. 209].

Describing precisely what happens to the output voltage in the overmodulating region is complex<sup>2</sup>, but one of the most influential factors is the frequency modulation index,  $m_f$ , defined in Equation 2.10, which, in conjunction with the amplitude modulation index, affects the output voltage of the inverter.

$$m_f = \frac{f_s}{f_1} \tag{2.10}$$

Various sources of literature provide varying perspectives on the overmodulating region. However, the primary reference source for this project recommends the carrier signal and control signal to be synchronized with each other to limit the harmonic content. This is achieved by utilizing values of  $m_f \leq 21$  [3, p. 208], which contrasts with the linear region where modulation is largely unaffected by  $m_f$ , at least for  $m_f > 9$  [3, p. 209].

$<sup>^{2}</sup>$  A methodology for estimating the amplitude modulation index within the nonlinear region is provided herein [2].

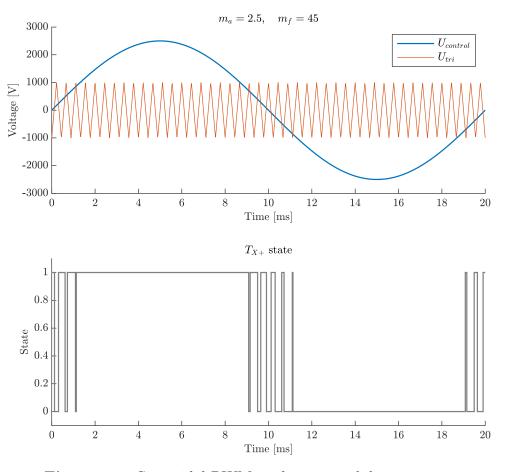

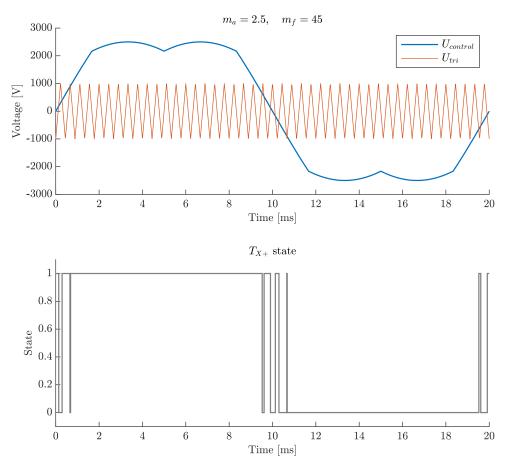

Figure 2.4: Sinusoidal PWM in the overmodulating region. Source: Created using MATLAB.

Figure 2.4 depicts a graphical representation of a modulating signal at a frequency of 50 Hz, exhibiting an amplitude modulation index of 2.5. Notably, the illustration demarcates the critical region of overmodulation, wherein the amplitude of the control signal exceeds that of the carrier signal. Such a condition results in the transistors remaining in a fixed state for extended periods, thereby generating harmonic frequencies.

#### Square Wave Operation

When the above is combined with the control signal being of a sufficiently high magnitude compared to the carrier signal  $(m_a \gg 1.0)$ , the output voltage is no longer composed of pulse width modulated transistor switches, and the inverter transitions into square wave operation. In this mode of operation, the output voltage peak is limited to  $4/\pi$  of half the DC-link voltage, as expressed by the following equation:

$$\hat{U}_{Xo1} = \frac{4}{\pi} \cdot \frac{U_d}{2}, \qquad m_a \gg 1.0$$

(2.11)

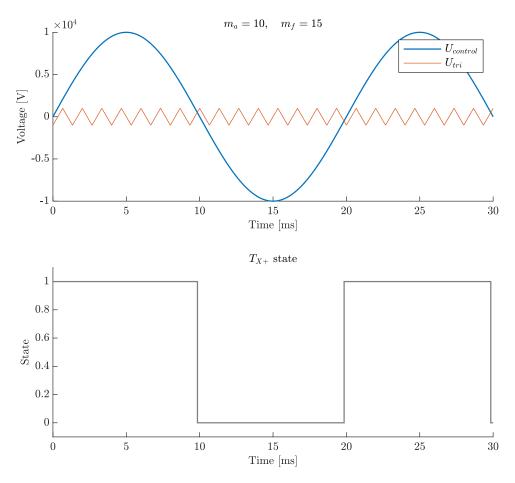

Figure 2.5 is plotted for 3/2 periods of the same modulating signal as in Figure 2.4, illustrating the behavior of the transistor signals as the control signal reaches a level where the carrier signal intersects it solely at the sinusoidal zero-crossing.

Figure 2.5: Sinusoidal PWM in square wave operation. Source: Created using MATLAB.

As can be observed from the figure, the transistors are triggered only twice during a period, which is advantageous in high-power applications with slower turn-on and turn-off speeds [3, p. 210], but impractical in a design where control of speed and torque of electric induction motors is desired. This is because of the limitation presented in Equation 2.11, which explicitly states that the output voltage can only be varied with the DC-link voltage.

## 2.3 Space Vector Pulse Width Modulation

Space Vector Pulse Width Modulation (SV-PWM) is a more advanced modulation technique frequently employed in three-phase inverters. It effectively addresses the drawbacks of conventional Pulse Width Modulation techniques, including the Sinusoidal PWM algorithm, by optimizing the usage of the available DC-link voltage. This modulation technique enables a higher amplitude modulation index relative to SPWM, resulting in an increased output voltage beyond the achievable limits of SPWM.

## Working Principle

The Space Vector Pulse Width Modulation technique functions the same way as SPWM by comparing a sinusoidal control signal,  $U_{control}$ , and a triangular carrier signal,  $U_{tri}$ , to determine the states of the individual transistors. The fundamental frequency,  $f_1$ , of the output voltage from the inverter is still determined by the control signal's frequency within the period  $T_s$ , while the triangular waveform's frequency establishes the switching frequency,  $f_s$ .

Although SV-PWM and SPWM share similarities in their basic operating principles, they diverge in the shape of the control signal throughout the period. Specifically, SV-PWM introduces a third harmonic component into the sinusoidal control signal, resulting in a more complex waveform, as depicted in Figure 2.6. The inclusion of such a harmonic component enhances the utilization of the DC-link voltage,  $U_d$ , by allowing a higher amplitude modulation index<sup>3</sup>,  $m_a$ .

$<sup>^3</sup> m_a > 1.0$  is still defined as overmodulation.

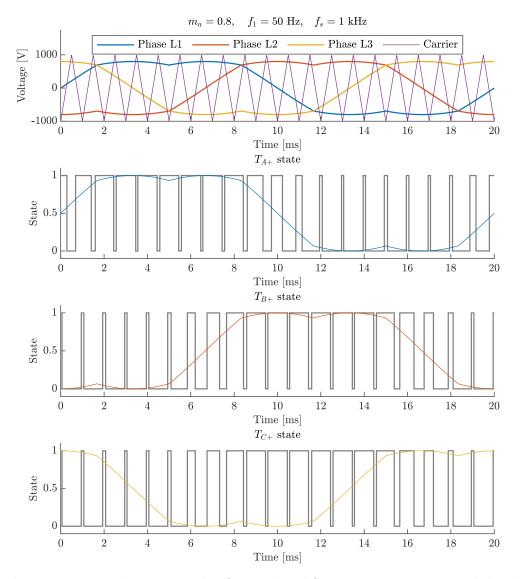

Figure 2.6: Working principle of a two-level Space Vector PWM modulated inverter. Source: Created using MATLAB.

As can be seen from the figure, the states of the upper and lower transistors,  $T_{X+}$  and  $T_{X-}$ , are determined based on the same comparison criteria presented in Equation 2.5, where  $U_{control} > U_{tri}$  indicates that the upper transistor conducts, whereas  $U_{control} < U_{tri}$  implies that the lower one conducts. Similar to the technique of SPWM, there exists no situation where the upper and lower transistors possess an identical state, regardless of the leg. Hence, there are two distinct states for each of the three legs, leading to a total of  $2^3 = 8$  possible combinations of the control signals, as illustrated in Table 2.1 [8, p. 121].

| Vector      | State                          | Voltage                                                     |

|-------------|--------------------------------|-------------------------------------------------------------|

| $ec{u}_0$   | $\vec{u}_{s}\left(000 ight)$   | $0\mathrm{V}$                                               |

| $ec{u}_1$   | $\vec{u}_{s}\left(001 ight)$   | $U_d e^{j0} = U_d \angle 0^\circ \mathrm{V}$                |

| $ec{u}_2$   | $\vec{u}_{s}\left(010 ight)$   | $U_d e^{j\frac{2\pi}{3}} = U_d \angle 120^\circ \text{ V}$  |

| $ec{u}_3$   | $\vec{u}_{s}\left(011 ight)$   | $U_d e^{j\frac{\pi}{3}} = U_d \angle 60^\circ \text{ V}$    |

| $ec{u}_4$   | $\vec{u}_s \left( 100 \right)$ | $U_d e^{j\frac{4\pi}{3}} = U_d \angle -120^\circ \text{ V}$ |

| $ec{u}_5$   | $\vec{u}_s\left(101\right)$    | $U_d e^{j\frac{5\pi}{3}} = U_d \angle -60^\circ \text{ V}$  |

| $ec{u}_6$   | $\vec{u}_s (110)$              | $U_d e^{j\pi} = U_d \angle 180^\circ \text{ V}$             |

| $\vec{u}_7$ | $\vec{u}_{s}\left(111 ight)$   | $0\mathrm{V}$                                               |

Table 2.1: Zero and basic voltage vectors for a two-level inverter.

Each binary digit within the system represents the states of the transistors associated with each leg within the inverter. A binary value of 1 signifies that the upper transistor is conducting, while a binary value of 0 indicates that the lower transistor is conducting. By alternation between these two states, it becomes possible to synthesize an average voltage space vector, as elaborated upon in the subsequent subsections.

#### Voltage Space Vectors

Unlike SPWM which employs three modulators to generate an equivalent number of phase voltages, SV-PWM utilizes a single modulator known as a reference voltage space vector, represented as  $\vec{u}_s$ . This vector is the vector sum of the three sinusoidal waveforms known from a conventional three-phase design, with each phase being 120 degrees apart, as shown in Equation 2.12 [8, p. 119]. Consequently, the magnitude of the reference voltage vector typically remains constant regardless of its spatial angle, denoted by  $\theta_s$ , that determines its location within the time period,  $T_s$ .

$$\vec{u}_{s}(t) = U_{Ao}(t) e^{j0} + U_{Bo}(t) e^{j\frac{2\pi}{3}} + U_{Co}(t) e^{j\frac{4\pi}{3}}$$

$$= U_{Ao}(t) \angle 0^{\circ} + U_{Bo}(t) \angle 120^{\circ} + U_{Co}(t) \angle -120^{\circ}$$

(2.12)

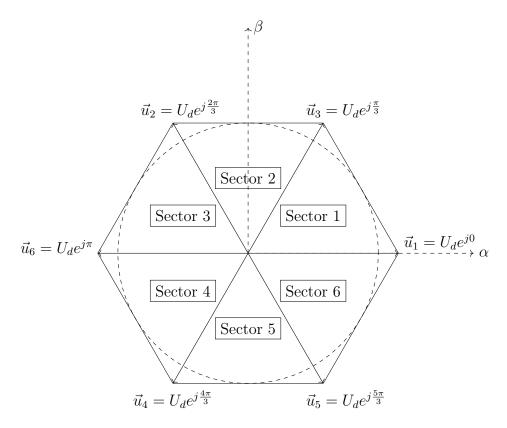

The speed at which the vector rotates from 0 to 360 degrees defines the fundamental frequency,  $f_1$ , of the three sinusoidal voltages that are generated. Along its path, the vector transverses six distinct sectors, each separated by a 60-degree displacement and bound by their neighboring basic voltage vectors,  $\vec{u}_{1-6}$ , as depicted in Figure 2.7. It is noteworthy that the two zero vectors,  $\vec{u}_0(000)$  and  $\vec{u}_7(111)$ , are absent from the illustration.

Figure 2.7: Basic voltage vector hexagon (zero vectors not shown). Source: Created using CircuiTikZ.

Every basic vector denotes the state of a leg with respect to the conductance of the six transistors, or alternatively, the level of voltage being emitted from the DC-link  $U_d$ . Notably, a comparison between the positional arrangement of the basic vectors illustrated in Figure 2.7 and their corresponding states as presented in Table 2.1 indicates that the SV-PWM algorithm attains a heightened level of energy efficiency, especially in terms of switching losses. This is attributed to the fact that each transition necessitates a change in switch state in only one of the legs.

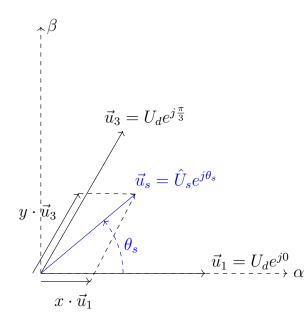

## Synthesizing Output Voltage

The average voltage space vector,  $\vec{u}_s^a$ , can be synthesized over the time interval  $T_s$  by computing the durations  $\underbrace{xT_s \text{ and } yT_s}_{\alpha \text{ and } \beta \text{ axis}}$ , which correspond to the periods during which the two neighboring basic vectors are active. In addition, it is necessary to determine the time period  $zT_s$ , during which the two zero vectors are active. For sector 1, shown in Figure 2.8, the average voltage space vector can be expressed using Equation 2.13 [8, p. 122].

Figure 2.8: Average voltage space vector in sector 1 ( $\theta_s = 40^\circ$ ). Source: Created using CircuiTikZ.

$$\vec{u}_{s}^{a} = \frac{1}{T_{s}} \left( xT_{s} \cdot \vec{u}_{1} + yT_{s} \cdot \vec{u}_{3} + zT_{s} \cdot 0 \right), \qquad x + y + z = 1$$

$$= x \cdot \vec{u}_{1} + y \cdot \vec{u}_{3}$$

(2.13)

Table 2.2 facilitates the derivation of Equation 2.13, as well as corresponding equations for the remaining five sectors, by means of the basic vector's amplitude,  $\hat{U}_s$ , and phase angle,  $\theta_s$ , relative to the alpha and beta axes, and the DC-link voltage [8, p. 123].

| Sector | Equation                                                                                      |

|--------|-----------------------------------------------------------------------------------------------|

| 1      | $\hat{U}_s e^{j\theta_s} = x \cdot U_d e^{j0} + y \cdot U_d e^{j\frac{\pi}{3}}$               |

| 2      | $\hat{U}_s e^{j\theta_s} = x \cdot U_d e^{j\frac{\pi}{3}} + y \cdot U_d e^{j\frac{2\pi}{3}}$  |

| 3      | $\hat{U}_s e^{j\theta_s} = x \cdot U_d e^{j\frac{2\pi}{3}} + y \cdot U_d e^{j\pi}$            |

| 4      | $\hat{U}_s e^{j\theta_s} = x \cdot U_d e^{j\pi} + y \cdot U_d e^{j\frac{4\pi}{3}}$            |

| 5      | $\hat{U}_s e^{j\theta_s} = x \cdot U_d e^{j\frac{4\pi}{3}} + y \cdot U_d e^{j\frac{5\pi}{3}}$ |

| 6      | $\hat{U}_s e^{j\theta_s} = x \cdot U_d e^{j\frac{5\pi}{3}} + y \cdot U_d e^{j0}$              |

Table 2.2: Average voltage space vector equations.

The equations presented in Table 2.2 are composed of a real component and an imaginary component. Utilizing Euler's formula<sup>4</sup>, these components can be expressed as products of cosine and sine functions, which can be further decomposed into their respective real and imaginary constituents. This implies that the duration at the  $\alpha$  and  $\beta$  coordinates  $\Re$  and  $\Im$  in each sector can be modeled by separate expressions, as elucidated in Table 2.3.

| Sector | $\Re(\hat{U}_s e^{j	heta_s})$                                                              | $\Im(\hat{U}_s e^{j	heta_s})$                                                                            |

|--------|--------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|

| 1      | $\hat{U}_s \cos \theta_s = x \cdot U_d + y \cdot U_d \cdot \frac{1}{2}$                    | $\hat{U}_s \sin \theta_s = y \cdot U_d \cdot \frac{\sqrt{3}}{2}$                                         |

| 2      | $\hat{U}_s \cos \theta_s = x \cdot U_d \cdot \frac{1}{2} - y \cdot U_d \cdot \frac{1}{2}$  | $\hat{U}_s \sin \theta_s = x \cdot U_d \cdot \frac{\sqrt{3}}{2} + y \cdot U_d \cdot \frac{\sqrt{3}}{2}$  |

| 3      | $\hat{U}_s \cos \theta_s = -x \cdot U_d \cdot \frac{1}{2} - y \cdot U_d$                   | $\hat{U}_s \sin \theta_s = x \cdot U_d \cdot \frac{\sqrt{3}}{2}$                                         |

| 4      | $\hat{U}_s \cos \theta_s = -x \cdot U_d - y \cdot U_d \cdot \frac{1}{2}$                   | $\hat{U}_s \sin \theta_s = -y \cdot U_d \cdot \frac{\sqrt{3}}{2}$                                        |

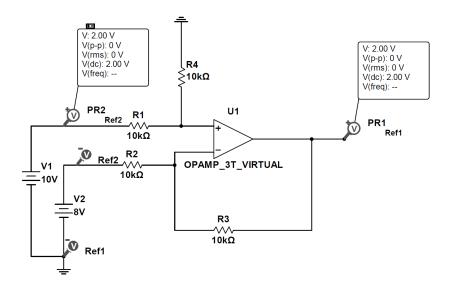

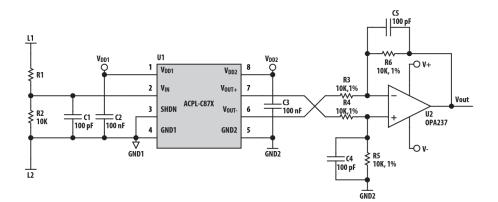

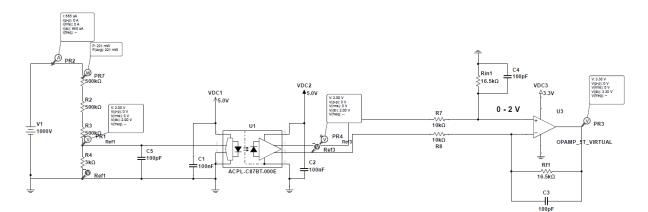

| 5      | $\hat{U}_s \cos \theta_s = -x \cdot U_d \cdot \frac{1}{2} + y \cdot U_d \cdot \frac{1}{2}$ | $\hat{U}_s \sin \theta_s = -x \cdot U_d \cdot \frac{\sqrt{3}}{2} - y \cdot U_d \cdot \frac{\sqrt{3}}{2}$ |