## Bachelor thesis:

# FPGA solution for communication between IPbus and a power control unit using a custom USART

Martin Eggen Jakob Hauser

28/05/2022

## **Document control**

| Thesis title:                                             | Date/Version              |

|-----------------------------------------------------------|---------------------------|

| FPGA solution for communication between IPbus and a power | 28. May. 2022 / 1.10      |

| control unit using a custom USART                         | Report number:            |

|                                                           | BO22EB-08                 |

| Authors:                                                  | Study:                    |

| Martin Eggen                                              | 19HEEL                    |

| martineggen99@gmail.com                                   | The number of pages       |

|                                                           | including attachments: 53 |

| Jakob Hauser                                              |                           |

| jakob.hauser72@gmail.com                                  |                           |

| HVL's supervisor/guide:                                   | Grading:                  |

| Svein Haustveit                                           | Open                      |

| svein.haustveit@hvl.no                                    |                           |

|                                                           |                           |

| Other notes:                                              |                           |

| We accept that the report may be published                |                           |

| Client:                                                      | Clients reference: |

|--------------------------------------------------------------|--------------------|

| Department of Physics and Technology - University of Bergen  | BO22EB-08          |

| The client's contact person (including contact information): |                    |

| Johan Alme                                                   |                    |

| +47 55 58 28 71                                              |                    |

| johan.alme@uib.no                                            |                    |

|                                                              |                    |

| Revision | Date          | Status           | Performed by                |

|----------|---------------|------------------|-----------------------------|

| 0.10     | 26. Apr. 2022 | First draft.     | Martin Eggen & Jakob Hauser |

| 0.20     | 3. May 2022   | Second draft.    | Martin Eggen & Jakob Hauser |

| 0.21     | 6. May 2022   | Restructure.     | Martin Eggen & Jakob Hauser |

| 0.30     | 19. May 2022  | Third draft.     | Martin Eggen & Jakob Hauser |

| 1.00     | 26. May 2022  | Release draft.   | Martin Eggen & Jakob Hauser |

| 1.10     | 27. May 2022  | Release version. | Martin Eggen & Jakob Hauser |

First and foremost, we would like to thank our supervisor, Professor Johan Alme, for being a great supervisor. Helping us throughout our whole project of writing this bachelor. From the very start, he was very helpful and encouraging giving us a good start to the project. He could help us with every part of the process as well. No matter if it was giving technical advice, teaching about GitHub and Linux, or helping us write the thesis.

We also want to thank our project neighbours Birger Olsen and Håvard Birkenes for being very active in the project, and always prepared to do joint testing or problem-solving. As well as being very helpful and willing to help, when asked about parts of the project.

A big thanks also has to go to our long-time lecturer and supervisor, Assistant Professor Svein Haustveit, for giving us the necessary knowledge to fulfil our task at hand. Teaching us to look at VHDL code as physical circuits rather than just code. Giving us a more in-depth understanding of how our written code would translate to circuitry.

## Abstract

The proton Computed Tomography (pCT) project in Bergen is a project aiming on designing a CT-scanner prototype using protons instead of photons. The current solution is using multiple layers of Monolithic Active Pixel chips (MAPS), called ALPIDE, to create a three-dimensional image scan. The ALPIDEs were developed at CERN for the inner Tracking System in a large ion collider experiment (ALICE).

A stable and reliable power supply chain is needed during operation. For that, a power supply is used for each layer, distributing even power to all layers. Custom PCBs housing microcontrollers are installed between the power supplies and the sensor layers. The PCBs are named Power Control Units (PCU). They are responsible for enabling the power to the layers and cutting the power if monitored currents, voltages or temperatures exceed programmable thresholds. An Ethernet connection is set up between the FPGA board and the control room computers, using a special protocol called IPbus developed at CERN. The PCUs use a custom Synchronous/Asynchronous Receiver/Transmitter Universal (USART) protocol for communication with the FPGA board. This thesis is a detailed VHDL solution for the FPGA that is responsible for this communication. The design consists of multiple different components that are to function on their own as well as in combination. For each component, a testbench is made, and documentation is presented. In the tests, the UVVM library [1] has been used to provide a structured methodology. The work is also available in a git repository [2].

The thesis contains a complete, and functioning solution for communication between IPbus and multiple USART slaves. In addition, two additional modules are planned for the design: (1) a version module including a version number and the git hash from the repository, and (2) a local housekeeping unit monitoring board-specific parameters such as current consumptions, voltage levels and temperatures. These modules were not realized due to time constraints.

The design has been simulated and verified using structural verification methodology. Hardware tests using an IPbus connection and preliminary versions of the PCU have also been conducted. These tests prove the design is operating as specified by the requirements.

| ALICE | E - A Large Ion Collider Experiment |                                                                      |

|-------|-------------------------------------|----------------------------------------------------------------------|

| BUS   | -                                   | Electrical conductors that carry digital signals between components  |

| DUT   | -                                   | Device Under Testing                                                 |

| FPGA  | -                                   | Field-programmable gate array                                        |

| GUI   | -                                   | Graphical User Interface                                             |

| HW    | -                                   | Hardware                                                             |

| I2C   | -                                   | Inter-Integrated Circuit                                             |

| IPbus | -                                   | Control link by CERN                                                 |

| LED   | -                                   | Light-Emitting Diode                                                 |

| LSB   | -                                   | Least Significant Bit                                                |

| LVDS  | -                                   | Low-voltage differential signalling                                  |

| MCU   | -                                   | Microcontroller                                                      |

| MJCU  | -                                   | Martin & Jakob's Communication Unit                                  |

| MSB   | -                                   | Most Significant Bit                                                 |

| MUX   | -                                   | Multiplexer (digital logic)                                          |

| РСВ   | -                                   | Printed Circuit Board                                                |

| рСТ   | -                                   | Proton Computed Tomography                                           |

| PCU   | -                                   | Power Control Unit                                                   |

| PSU   | -                                   | Power Supply Unit                                                    |

| SOBP  | -                                   | Spread-Out Bragg Peak                                                |

| SW    | -                                   | Software                                                             |

| UiB   | -                                   | Universitetet i Bergen                                               |

| USART | -                                   | Universal Synchronous/Asynchronous Receiver/Transmitter              |

| UVVM  | -                                   | Universal VHDL Verification Methodology                              |

| VHDL  | -                                   | The Very High-Speed Integrated Circuit Hardware Description Language |

## Acronyms

## **Table of Contents**

| D  | ocumer    | nt contr | ol                               | . 2 |

|----|-----------|----------|----------------------------------|-----|

| A  | cknowl    | edgeme   | nts                              | . 3 |

| A  | bstract   |          |                                  | . 4 |

| A  | cronym    | IS       |                                  | . 5 |

| Li | st of Fig | gures    |                                  | . 8 |

| Li | st of Lis | stings   |                                  | . 9 |

| Li | st of ta  | bles     |                                  | . 9 |

| 0  | utline    |          |                                  | 10  |

| 1  | Intro     | oductio  | n                                | 11  |

|    | 1.1       | Particl  | e Therapy                        | 11  |

|    | 1.1.      | 1        | Medical Imaging Methods          | 12  |

|    | 1.2       | The Be   | ergen protonCT Project           | 13  |

|    | 1.3       | Requir   | ements                           | 16  |

| 2  | Rela      | ated wo  | rk                               | 17  |

|    | 2.1       | IPbus .  |                                  | 17  |

|    | 2.2       | Conne    | cted projects                    | 20  |

|    | 2.2.      | 1        | The Control room                 | 20  |

|    | 2.2.      | 2        | The Power Control Unit           | 20  |

| 3  | Prol      | blem an  | alysis                           | 21  |

| 4  | Des       | ign      |                                  | 22  |

|    | 4.1       | MJCU     | – top-level                      | 23  |

|    | 4.2       | com_n    | nodule                           | 24  |

|    | 4.2.      | 1        | com_module_reg                   | 25  |

|    | 4.2.      | 2        | com_module_fifo                  | 29  |

|    | 4.2.      | 3        | com_module_usart                 | 31  |

|    | 4.3       | global_  | _module                          | 34  |

|    | 4.4       | dumm     | y_module                         | 35  |

|    | 4.5       | versio   | n_module and housekeeping_module | 35  |

|    | 4.5.      | 1        | Version_module                   | 35  |

|    | 4.5.      | 2        | Housekeeper_module               | 35  |

| 5  | Test      | ts and v | erification                      | 36  |

|    | 5.1       | Verific  | ation                            | 36  |

|    | 5.1.3  | 1       | UVVM                                        | 37 |

|----|--------|---------|---------------------------------------------|----|

|    | 5.1.2  | 2       | DO-file                                     | 39 |

| 5  | 5.2    | Hardwa  | are testing                                 | 39 |

| 6  | Disc   | ussion  |                                             | 13 |

| 7  | Con    | clusion | and Outlook                                 | 14 |

| 7  | 7.1    | Conclu  | sion                                        | 14 |

| 7  | 7.2    | Outloo  | k ۷                                         | 14 |

| 8  | Bibli  | ography | y                                           | 45 |

| Ар | pendix | A       | Development tools                           | 16 |

| Ар | pendix | В       | Address map for all modules inside the MJCU | 17 |

|    |        |         | A.1 Module addresses                        | 17 |

|    |        |         | A.2 Address map                             | 18 |

| Ap | pendix | C C     | DATA FLOW                                   | 50 |

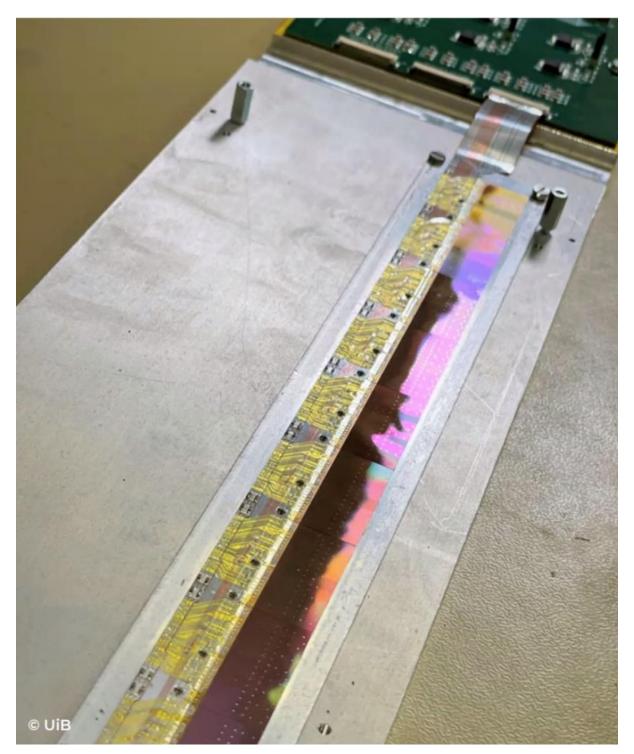

| Ap | pendix | D       | Picture of an ALPIDE sensor                 | 52 |

| Ар | pendix | E       | Project plan                                | 53 |

## **List of Figures**

| Figure 1 - Graphical illustration of how the dose is delivered to the tissue [3]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 11                                                       |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

| Figure 2 - Simplified CAD of the pCT instrument                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 13                                                       |

| Figure 3 – Bergen pCT project overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 14                                                       |

| Figure 4 - Simplified overview of the pCT power control system                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 14                                                       |

| Figure 5 – power control unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                          |

| Figure 6 – PCU connected to a power supply unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 15                                                       |

| Figure 7 - The Xilinx KCU105Evaluation Board [4]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 16                                                       |

| Figure 8 - ipbus implemented in a top-file                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 17                                                       |

| Figure 9 - ipbus_fabric_sel with modules connected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 18                                                       |

| Figure 10 - powermonitor repository - folder structure inside each module                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 22                                                       |

| Figure 11 - Block diagram of MJCU as payload                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 23                                                       |

| Figure 12 - com_module block diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 24                                                       |

| Figure 13 - IPbus wait state slaves                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 25                                                       |

| Figure 14 – zero-wait state read                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 26                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                          |

| Figure 15 – zero-wait state write                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 27                                                       |

| Figure 15 – zero-wait state write                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 27<br>29                                                 |

| Figure 15 – zero-wait state write<br>Figure 16 - part one in a pointer-based FIFO illustration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 27<br>29<br>29                                           |

| Figure 15 – zero-wait state write<br>Figure 16 - part one in a pointer-based FIFO illustration<br>Figure 17 – part two in a pointer-based FIFO illustration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 27<br>29<br>29<br>30                                     |

| Figure 15 – zero-wait state write<br>Figure 16 - part one in a pointer-based FIFO illustration<br>Figure 17 – part two in a pointer-based FIFO illustration<br>Figure 18 - part three in a pointer-based FIFO illustration                                                                                                                                                                                                                                                                                                                                                                                                                         | 27<br>29<br>29<br>30<br>30                               |

| Figure 15 – zero-wait state write<br>Figure 16 - part one in a pointer-based FIFO illustration<br>Figure 17 – part two in a pointer-based FIFO illustration<br>Figure 18 - part three in a pointer-based FIFO illustration<br>Figure 19 - part four in a pointer-based FIFO illustration                                                                                                                                                                                                                                                                                                                                                           | 27<br>29<br>29<br>30<br>31                               |

| <ul> <li>Figure 15 – zero-wait state write</li> <li>Figure 16 - part one in a pointer-based FIFO illustration.</li> <li>Figure 17 – part two in a pointer-based FIFO illustration.</li> <li>Figure 18 - part three in a pointer-based FIFO illustration.</li> <li>Figure 19 - part four in a pointer-based FIFO illustration.</li> <li>Figure 20 - Custom USART protocol between the FPGA and PCUs.</li> </ul>                                                                                                                                                                                                                                     | 27<br>29<br>30<br>30<br>31<br>32                         |

| <ul> <li>Figure 15 – zero-wait state write</li> <li>Figure 16 - part one in a pointer-based FIFO illustration</li> <li>Figure 17 – part two in a pointer-based FIFO illustration</li> <li>Figure 18 - part three in a pointer-based FIFO illustration</li> <li>Figure 19 - part four in a pointer-based FIFO illustration</li> <li>Figure 20 - Custom USART protocol between the FPGA and PCUs</li> <li>Figure 21 – The state machine in com_module_usart</li> </ul>                                                                                                                                                                               | 27<br>29<br>30<br>30<br>31<br>32<br>36                   |

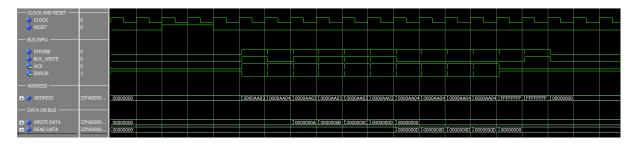

| <ul> <li>Figure 15 – zero-wait state write</li> <li>Figure 16 - part one in a pointer-based FIFO illustration</li> <li>Figure 17 – part two in a pointer-based FIFO illustration</li> <li>Figure 18 - part three in a pointer-based FIFO illustration</li> <li>Figure 19 - part four in a pointer-based FIFO illustration</li> <li>Figure 20 - Custom USART protocol between the FPGA and PCUs</li> <li>Figure 21 – The state machine in com_module_usart</li> <li>Figure 22 - Example of a wave diagram from a small testbench</li> </ul>                                                                                                         | 27<br>29<br>30<br>30<br>31<br>32<br>36<br>40             |

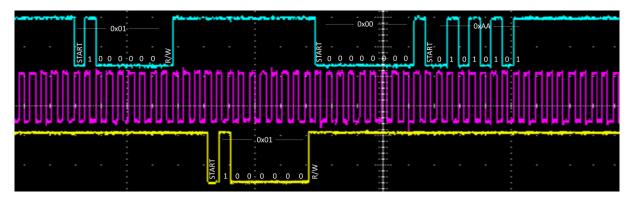

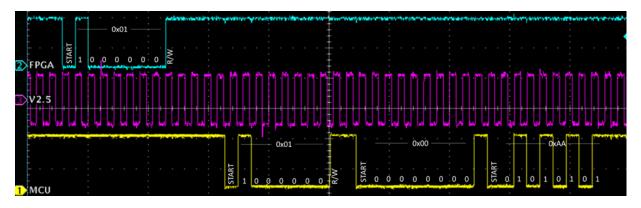

| Figure 15 – zero-wait state write<br>Figure 16 - part one in a pointer-based FIFO illustration<br>Figure 17 – part two in a pointer-based FIFO illustration<br>Figure 18 - part three in a pointer-based FIFO illustration<br>Figure 19 - part four in a pointer-based FIFO illustration<br>Figure 20 - Custom USART protocol between the FPGA and PCUs<br>Figure 21 – The state machine in com_module_usart.<br>Figure 22 - Example of a wave diagram from a small testbench<br>Figure 23 - MJCU writing 0x00AA to PCU-address 0x01 (asynchronous)                                                                                                | 27<br>29<br>30<br>30<br>31<br>32<br>36<br>40<br>40       |

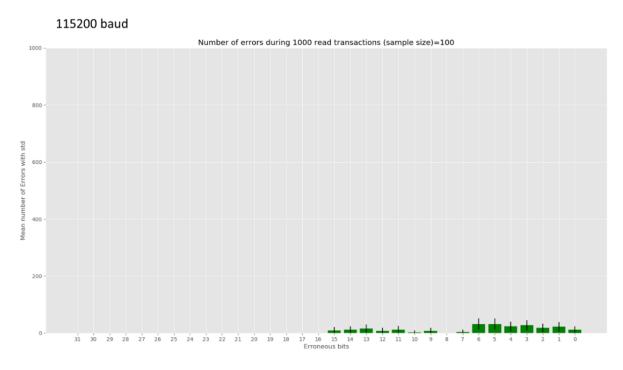

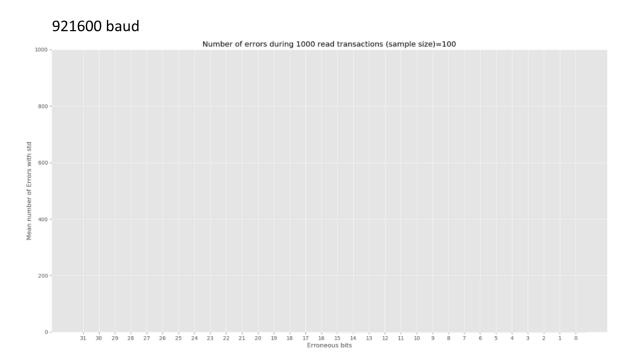

| Figure 15 – zero-wait state write<br>Figure 16 - part one in a pointer-based FIFO illustration<br>Figure 17 – part two in a pointer-based FIFO illustration<br>Figure 18 - part three in a pointer-based FIFO illustration<br>Figure 19 - part four in a pointer-based FIFO illustration<br>Figure 20 - Custom USART protocol between the FPGA and PCUs<br>Figure 21 – The state machine in com_module_usart<br>Figure 22 - Example of a wave diagram from a small testbench<br>Figure 23 - MJCU writing 0x00AA to PCU-address 0x01 (asynchronous)<br>Figure 25 - Mean bit error using 115200 baud<br>Figure 26 - Mean bit error using 921600 baud | 27<br>29<br>30<br>30<br>31<br>32<br>36<br>40<br>42<br>42 |

| Figure 15 – zero-wait state write<br>Figure 16 - part one in a pointer-based FIFO illustration<br>Figure 17 – part two in a pointer-based FIFO illustration<br>Figure 18 - part three in a pointer-based FIFO illustration<br>Figure 19 - part four in a pointer-based FIFO illustration<br>Figure 20 - Custom USART protocol between the FPGA and PCUs<br>Figure 21 – The state machine in com_module_usart<br>Figure 22 - Example of a wave diagram from a small testbench<br>Figure 23 - MJCU writing 0x00AA to PCU-address 0x01 (asynchronous)<br>Figure 25 - Mean bit error using 115200 baud                                                 | 27<br>29<br>30<br>30<br>31<br>32<br>36<br>40<br>42<br>42 |

| Listing 1 - Connecting a slave to IPbus | . 19 |

|-----------------------------------------|------|

| Listing 2 - How ACK follow strobe       |      |

| Listing 3 - IPbus slave - read process  |      |

| Listing 4 - IPbus slave -write process  |      |

| Listing 5 - IPbus slave - address map   |      |

| Listing 6 - UVVM log report             |      |

| Listing 7 - UVVM do-file                | . 38 |

## List of tables

| Table 1 - IPbus signals between master and slave [5]                                        | 18 |

|---------------------------------------------------------------------------------------------|----|

| Table 2 - address map com_module                                                            | 28 |

| Table 3 - Address map global_module                                                         | 34 |

| Table 4 - Address map dummy_module                                                          | 35 |

| Table 5 - Bit-error test with varying baud rates, performing 1000 read operations 100 times | 41 |

| Table 6 - Module addresses                                                                  | 47 |

| Table 7 - Address map for MJCU                                                              | 49 |

## Outline

**Chapter 1: Introduction.** This chapter contains an introduction to the project that this thesis is a part of. Also included are the requirements for the project connected to this thesis.

**Chapter 2: Related work.** The related work chapter focuses on giving background information on what work was needed for this project to work. IPbus is explained and given an introduction. Both adjacent master theses are also presented.

**Chapter 3: Problem analysis.** This is the start of the project. Problem analysis is an analysis of the requirements and the earlier work, to conclude with an idea on how to solve the task.

**Chapter 4: Design.** Designing the VHDL solution was the biggest part of creating a working solution. In this chapter, a detailed walkthrough of all the different components in this solution is given. As well as some in-depth information on the workings of each component.

**Chapter 5: Tests and verification.** In this chapter, the focus lies on what tests were performed on and around the project. Including what type of tests were performed, and what tools were used to perform said tests. Thereby looking into what UVVM is and why it was used.

**Chapters 6: Discussion**, and **Chapter 7: Conclusion and Outlook.** These chapters evaluate the work done in this thesis. Outlook also gives a discussion on the future work needed.

## **1** Introduction

#### **1.1 Particle Therapy**

Radiotherapy is the traditional form of cancer treatment using irradiation. In radiotherapy, high-energy electromagnetic radiation is used to kill cancer cells. Radiotherapy is an important method for cancer treatment. It can be used alone, or in combination with other methods like surgery, chemotherapy, and/or immunotherapy. The goal of the treatment is to damage the cancer cells either directly or indirectly. Stopping them from reproducing or causing them to die.

Sending ionizing radiation through the body is effective for killing cancer cells, but it also damages healthy cells in the process. Healthy tissue has an advantage over tumorous tissue though. It heals faster. Treatment is therefore distributed over multiple sessions of irradiation. Each dose administered is weak enough for the healthy tissue to recover in between the treatments. The photon beams are sent through the body from several directions to further spread out the damage. A high level of precision is important to make sure that the healthy tissue receives a low amount of radiation. With higher precision comes the possibility of safely increasing the dosage. Resulting in fewer sessions to complete the treatment.

The biological structure varies from tumour to tumour. It can even vary within a single tumour. Oxygen is a mediator for indirect damage to DNA. Parts of a tumour, which have reduced access to oxygen, can be more resistant to radiation. Samples, MR- and PET pictures are used to provide information about the tumour's biology. This makes it possible to individualize the treatment of different tumours [3].

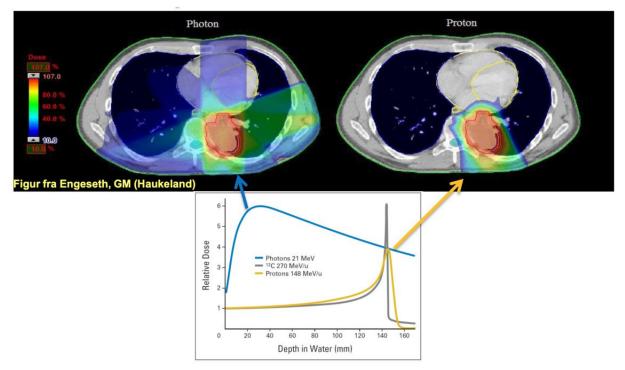

Figure 1 - Graphical illustration of how the dose is delivered to the tissue [3]

Particle therapy uses positively charged ions like protons or carbon ions instead of the traditional photons. This opens the possibility for treatment of delimited areas inside a patient, whilst damaging DNA more efficiently. Compared to radiotherapy, particle therapy results in fewer side effects such as organ damage or secondary cancers because it reduces the radiation to the surrounding tissue.

The two methods differ the most in how the energy is deposited in the tissue. Figure 1 shows how the energy is transferred using radio- and particle therapy.

The photons (blue) transfer a large amount of energy to the tissue a short distance after they penetrate the skin. Therefore, the tumour is radiated from different angles to achieve the correct amount of radiation. The yellow line illustrates how the protons deposit a major part of their energy directly into the tumour. This peak is called the Bragg peak. It can be adjusted to target where the tumour is located. The Bragg peak is not wide enough to cover the whole tumour. A modified beam is therefore created to get a broader range. This beam is called Spread-Out Bragg Peak (SOBP). The graph also shows the potential of using carbon-ions with an even more effective peak.

#### **1.1.1 Medical Imaging Methods**

#### Computed Tomography

A Computed Tomography (CT) scan combines multiple images taken from different angles of a body using beams of photons. The device is rotated around the body, and the body is moved horizontally to create a three-dimensional image.

#### Proton Computed Tomography

Proton Computed Tomography (pCT) uses protons instead of photons. The images are created by sending a beam of protons with enough energy to pass directly through the patient so that the Bragg peak ends up in the calorimeter. This reduces the amount of irradiated tissue. The protons will interact with electrons and/or the nuclei of an atom. These interactions will cause them to change paths. The path of the protons after exiting the body is then reconstructed from the data collected by the calorimeter.

It is possible to achieve higher accuracy when using pCT-scanning for dose planning compared to a CT scan. Currently, the proton treatment is estimated by the Houndsfield units from CT scanning. This estimation causes an error of 2-3% [3]. This implies that by using proton CT, less of the healthy tissue will be irradiated and the risk of late effects is reduced.

## **1.2 The Bergen protonCT Project**

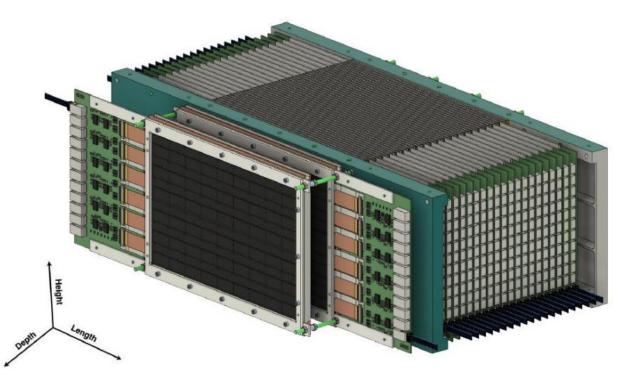

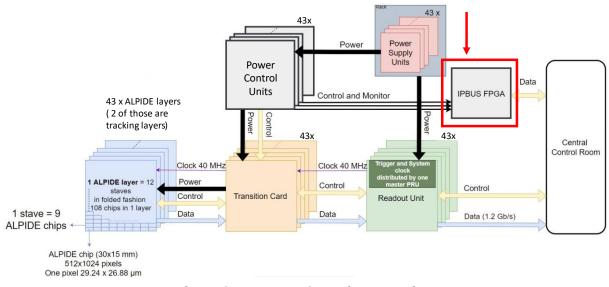

The University of Bergen is the leading part of the Bergen proton CT project. The project consists of multiple parts, as shown in Figure 3. The main part of this project is the calorimeter depicted in Figure 2. It is made out of 43 layers with 108 ALPIDE sensors on each layer. They are monolithic active pixel sensors (MAPS) created for the CERN ALICE experiment. These layers are responsible for collecting information about the proton's velocity and position.

Figure 2 - Simplified CAD of the pCT instrument

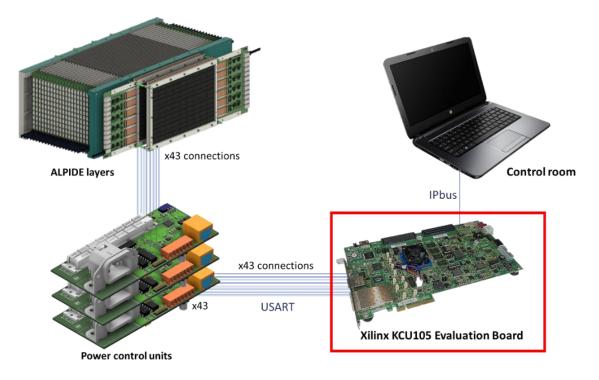

Each of the layers is connected to individual transition cards and custom power control units (PCU) that deliver the power from the power supply units (PSU) to the layer. This thesis is aimed to make a system that could write and read information to and from the PCUs and forward it to a computer inside the control room. An FPGA board is being used to achieve this.

Figure 3 – Bergen pCT project overview

Figure 4 shows how the different components in the pCT power control system are connected to this thesis. The computer in the control room connects to the FPGA board with an ethernet cable using the IPbus protocol. The FPGA board is connected to 43 PCUs via ethernet cables, using a custom USART protocol for communication.

Figure 4 - Simplified overview of the pCT power control system

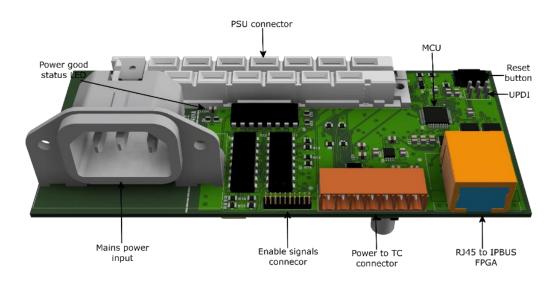

Figure 5 shows what in Figure 4 is labelled as "Power control units". These are the custommade circuit boards that transfer power from the PSUs (shown in Figure 6) to the ALPIDE layers. The connections are depicted in Figure 3. 43 of these boards will be connected to the FPGA board through an RJ45 rack.

The PCUs have full control over the power given to the ALPIDE layers by the PSUs. They can control the maximum voltage and current on its outputs and shut down the connected layer if a maximum temperature is reached. All the information about different values and thresholds is available to read and modify by the user through the FPGA.

Figure 5 – power control unit

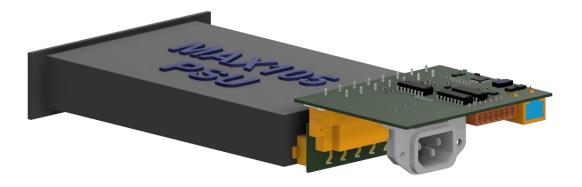

Figure 6 – PCU connected to a power supply unit

## **1.3 Requirements**

The prime objective of this thesis is to make a stable communication link between a computer inside a control room (using IPbus by CERN) and 43 external devices (using a custom USART protocol). Designing it to be as stable and reliable as possible. Prioritizing stability over efficiency.

The requirements are as follows:

- FPGA design fit to a Xilinx KCU105 Evaluation Board containing

- An IPbus gateway.

- o A bus connected to multiple slaves containing

- 43 slaves for communication with external devices

- A global module overarching all 43 communication slaves

- A test module, for confirming functionality

- Slaves managing onboard functions and a version GitHash

- Developed using a type of GIT version control system.

- Developing every component with testbenches using the UVVM library.

- Good documentation for every part of the system.

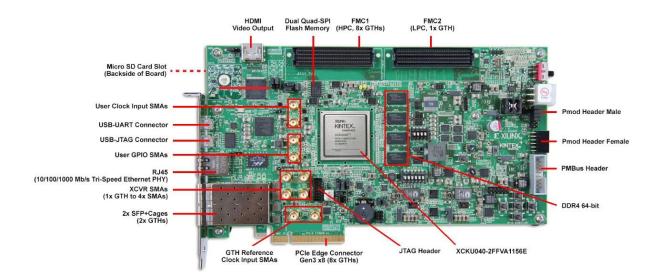

The Xilinx KCU105 Evaluation Board features the Kintex XCKU040-2FFVA1156E FPGA. It has all the I/O resources that would be necessary for this project. The required resources contain an RJ45 port for connecting to the control room, some GPIO for prototyping, and two FMC connectors (high/low pin-count) for connecting the PCUs.

Figure 7 - The Xilinx KCU105Evaluation Board [4]

#### 2.1 IPbus

IPbus is a packet-based control protocol made by CERN for communicating with addressaware hardware inside an FPGA [5]. They have made both the software and the firmware side that communicate with each other through 1Gbit ethernet. It does not support devices with auto-negotiation. The software side has a Control Hub that uses an IPbus reliability mechanism to correct for losses or duplications. The firmware side can be connected to multiple slaves made by a user, using high-performance and reliable connections.

The IPbus firmware module is an on-chip system. All the calculations and timings are being made and processed inside the FPGA chip. No external devices are needed. This makes it compatible with a wide range of FPGAs regardless of what type of sensors or circuitry surrounds the chip. It is designed to be a common module that can run by itself alongside a user's main code inside the same FPGA. This makes it easy to integrate into a project.

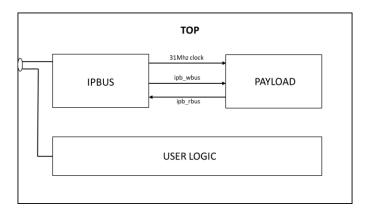

Figure 8 - ipbus implemented in a top-file

CERN has made several example designs for different development boards. This is currently made for Xilinx devices only, but the code is adaptable to fit onto Intel devices as well.

The firmware side of IPbus acts like a master within the FPGA and communicates with connected slaves located inside the PAYLOAD-block using a 31Mhz clock and seven signals shown in Table 1. These seven signals are located inside two types named *ipb\_wbus* and *ipb\_rbus*. *Ipb\_wbus* has all the signals going from master to slave, and *ipb\_rbus* got the ones going from slave to master. These signal types can be used to declare signals or ports like this:

| IPBUS_IN  | : in  | ipb_wbus; |

|-----------|-------|-----------|

| IPBUS_OUT | : out | ipb_rbus; |

The reduction of signals makes it easier to follow the routing of the signals between the different modules and components.

| -          |                 |       | -                                                            |

|------------|-----------------|-------|--------------------------------------------------------------|

| Signal     | Direction       | Width | Description                                                  |

| ipb_addr   | Master to slave | 32    | Bus address                                                  |

| ipb_wdata  | Master to slave | 32    | Data to be written to a slave                                |

| ipb_write  | Master to slave | 1     | Asserted for a write cycle, deserted for a read cycle        |

| ipb_strobe | Master to slave | 1     | Qualifies address and data; assertion marks start of a cycle |

| ipb_rdata  | Slave to master | 32    | Data read from a slave                                       |

| ipb_ack    | Slave to master | 1     | Acknowledge flag; assertion marks end of cycle               |

| ipb_err    | Slave to master | 1     | Bus error flag; assertion marks end of cycle                 |

Table 1 - IPbus signals between master and slave [5]

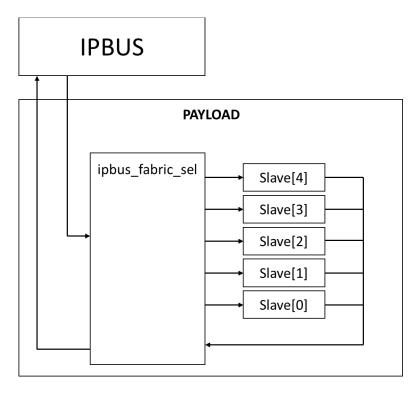

The slaves themselves do not need to handle the address signal from IPbus. This is handled by a component inside PAYLOAD named ipb\_fabric\_sel shown in Figure 9. Ipb\_fabric\_sel is responsible for which slave gets to communicate with the IPbus. This makes it possible to make slaves that do not know what address to respond to. They are just waiting for a strobe signal from fabric\_sel. As a result, all slaves can interpret the signals the same way. They just need to take care of any internal registers.

Figure 9 - ipbus\_fabric\_sel with modules connected

The implementation of fabric\_sel also makes it easier to add more slaves to the system if needed. Using the port map of the dummy\_module slave as an example:

```

-- Slave 67 : dummy_module

dummy_module : entity work.dummy_module

port map(

CLK => ipb_clk,

RST => ipb_rst,

IPBUS_IN => ipbw(67),

IPBUS_OUT => ipbr(67)

);

```

#### Listing 1 - Connecting a slave to IPbus

Dummy\_module will answer to module address 67 because it is connected to in- and output number 67 on fabric\_sel. If more slaves are introduced, they can be connected to pin 68, 69 and so on. They will then automatically answer to the corresponding module address.

## 2.2 Connected projects

In the previous chapter, a mention was given to the wider project that stretches beyond the borders of this assignment. Where in Figure 3 and Figure 4 a complete overview and a simplified view of the entirety of the project was shown. In relevance to the FPGA, the connecting parts of the project can be split into two parts. The "control room" and the "power control units". These two parts have each their own master student working on them.

#### 2.2.1 The Control room

The software for the control room is designed by Håvard Birkenes [6]. The control room as it is referred to is a computer connected to all information channels of the project. The section Håvard is responsible for contains all that is connected to the power control system. It is responsible for handling the control, configuration, and monitoring of the power system. The configuration data are stored in a MongoDB database, and the monitoring data are stored in a time-based database (inFluxDB). Grafana is used to visualize the monitored values.

Python is used as the design language in this part, and this enables the possibility to communicate with the API directly using script-based functions. This is extremely valuable in the test and development phase.

#### 2.2.2 The Power Control Unit

The PCU and the concept of the distributed power system is designed by Birger Olsen [7], Originally, the plan was that all layers should be powered by one large power supply, and there should be one central power control unit for all layers. However, the solution proposed by [7] proved cheaper, more elegant and easier to implement.

The PCU, which sits directly on the power supply, includes filters to reduce the power supply noise, as well as a microcontroller that enables the power to the sensor layers and monitors the currents, voltages and temperatures. Additionally, it contains programmable thresholds. The power is cut if the monitored values exceed these thresholds. This gives a short response time which is needed to avoid damage to the sensor layers and lowers the speed requirement for the rest of the power control system. Making it possible to prioritize reliability before speed. It is important to stress that since the sensor layers measure ionizing radiation, errors can be expected that for instance generates high current consumption due to single event effects in the sensors. Writing a design to an FPGA requires a VHDL design tool. In this case, since the selected FPGA is from Xilinx, we were given access to a program called Vivado. This was made available to us by the University in Bergen.

The Xilinx KCU105 Evaluation Board featuring the Kintex UltraScale XCKU040-2FFVA1156E FPGA was chosen on the premise that it featured everything that was needed in terms of IO-resources and FPGA. It was also the most convenient choice since other options would have to include a custom PCB design. The need for prototypes during development and the low quantity production would have led it to be more expensive than buying a finished product. This would also require a design team that would increase the costs even further.

With the requirements in mind, there are still multiple options on how to structure the VHDL design. The FPGA's task is to transfer data between a control room and the multiple power control units. One way of designing a system like this would be to make multiple components that take care of different requirements and then connecting them together. This way of design results in a tidy, and easy to test and troubleshoot. Each of the components can be verified in a controlled testbench. Making it easy to add more components in the future if needed. A goal of the design is to make it as efficient as possible, to make sure it's not the bottleneck of the system. One of the ways to accomplish this is to make sure the system can communicate with the PCUs in parallel. Since the solution is an FPGA design, it is possible to have the communication between one PCU take the same amount of time as communicating with all 43 of them at the same time. It is important to state that the system does not have a strict timing requirement. It is however important that the configuration time does not feel slow for the user, and that the monitoring is frequent enough. In this case, reliability is more important than speed. One of the ways to make it more reliable is by writing the data that has been written to a given address to the control room using what is called a handshake. The PCUs already have this as a built-in function in their custom USART protocol. It confirms which address was reached by sending a copy of the address back as soon as it is received. This confirmed address is then put together with the data received inside the FPGA to formulate a handshake to the control room as well.

Since this bachelor thesis is a part of a bigger system, it was important to make the project structured and understandable for other people that may modify or reuse it after this bachelor thesis has ended. UiB were already using a custom version of GitHub namely git.app.uib as a Git version control system. Which we used as well in the development of this project.

The project has multiple modules with independent testbenches and files, so it was important to keep everything organized and well structured. To be consistent with the naming of folders and components was also a high priority.

## 4 Design

The main essence of this project was to make an FPGA solution that would take in data from an already existing bus design (IPbus) and convert said data into a serial data transfer toward the PCUs, and the other way around. The protocol for the PCUs was made a few weeks after this project began but it was still prone to change.

It was made clear that the goal should not be to complete every requirement given, but to make sure everything that was constructed was working as intended. A lot of time went into the creation of testbenches because of this.

To make this project well-structured and easy to understand, each of the modules was created separately. This made it possible to connect them to different testbenches to show how the individual parts of the system worked. To make sure the git repository [2] was well structured, all the folders for the different modules got the same layout. Every module has its own folder including the subfolders components, scripts, source files (src) and testbench (tb). This makes navigating to the desired files easier, and each testbench can be compiled the same way. The reason structure is so important is because someone else should be able to do further work and development on it in the future if it is needed.

| Name         | Last commit            | Last update |

|--------------|------------------------|-------------|

|              |                        |             |

| 🗅 components | FIFO behaviour         | 1 week ago  |

| 🗅 scripts    | Update MJCU_tb log.txt | 1 week ago  |

| 🗅 src        | Update MJCU_pkg.vhd    | 4 days ago  |

| 🗅 tb         | FIFO behaviour         | 1 week ago  |

Figure 10 - powermonitor repository - folder structure inside each module

## 4.1 MJCU – top-level

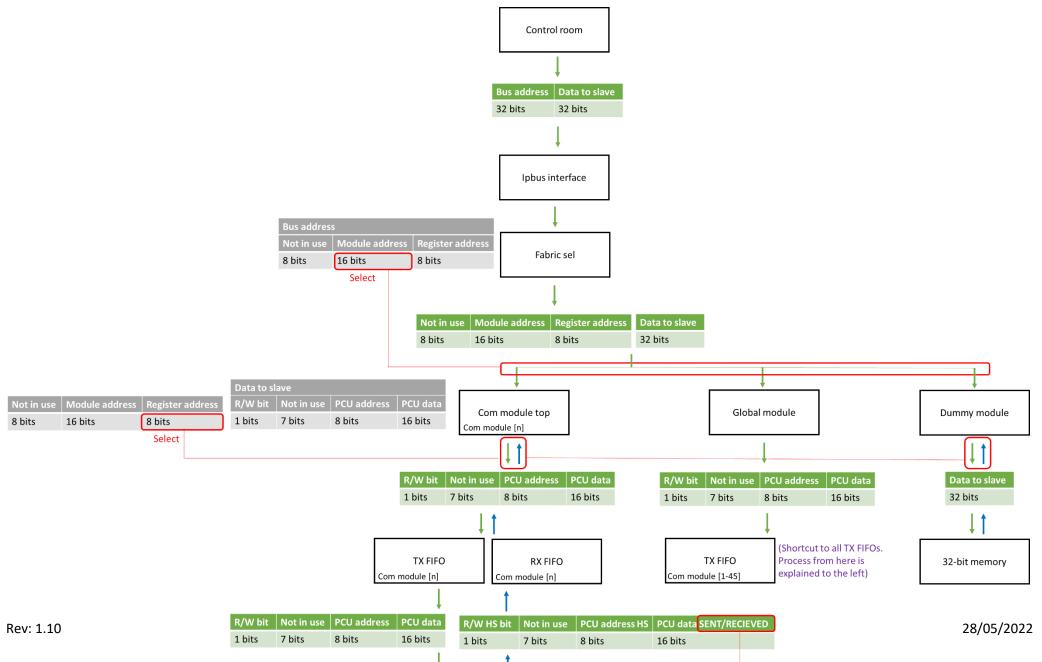

MJCU is an acronym for Martin and Jakob's Communication Unit. Figure 11 shows a simplified block diagram of how the modules are connected to each other, to IPbus and to the power control units. Since the modules have internal registers, a decision was made that ipb\_fabric\_sel should use *ipb\_addr(15 downto 8)* to determine which module to select. Leaving *Ipb\_addr(7 downto 0)* available for selecting internal registers inside the modules. This should give a sufficient amount of both potential slaves and slave addresses. The modules in this design are com\_module, global\_module and dummy\_module.

Figure 11 - Block diagram of MJCU as payload

## 4.2 com\_module

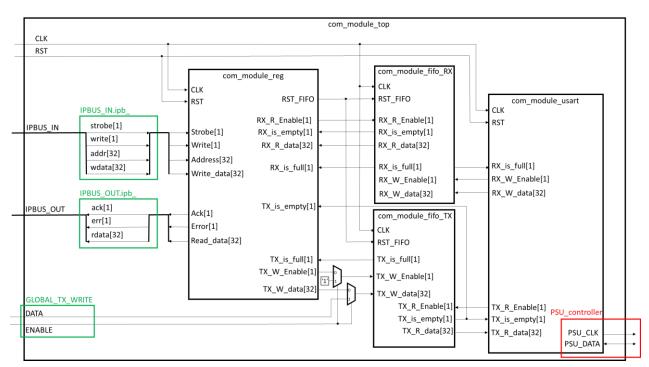

Com\_module is short for communication module. It is the largest of the modules in this design and is responsible for communicating with the power control units. This module is meant to be duplicated as many times as the amount of power control units connected to the system. One com\_module will be connected to one PCU.

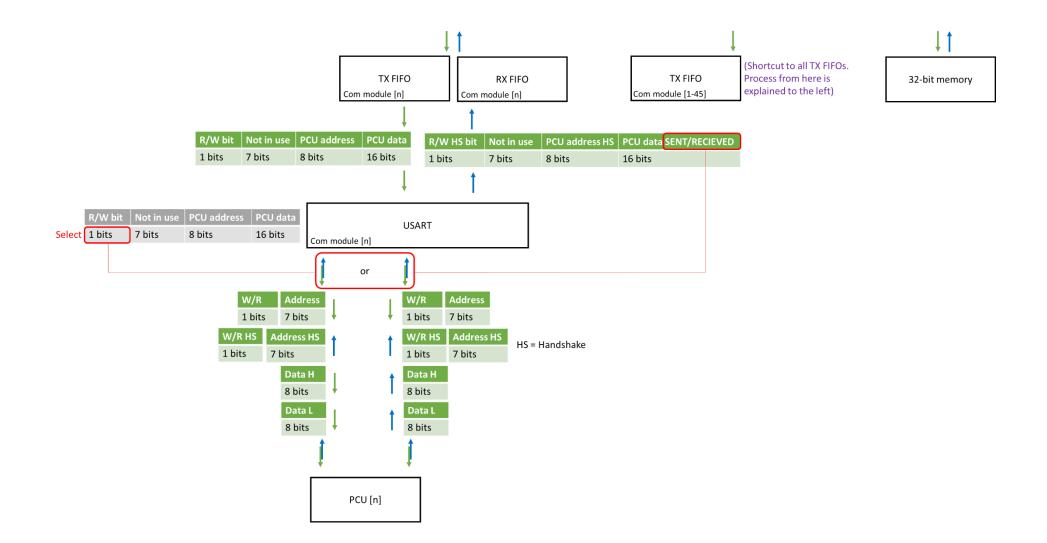

Com\_module consists of four components. Com\_module\_reg, two com\_module\_fifos and com\_module\_usart. Com\_module\_reg handles the communication with IPbus. It can read data from one com\_module\_fifo and write to the other. FIFO stands for "First In First Out", and is used to temporary queue up data. Every com\_module has two FIFOs. One for the data from com\_module\_reg to com\_module\_usart (TX\_FIFO), and one for the data from com\_module\_usart to com\_module\_reg (RX\_FIFO). Com\_module\_usart communicates with a power control unit using a custom 8-bit USART protocol. This protocol sends data in bulks of 8 bits, one bit at a time with a start bit for every transaction. The bits are being sent with a given baud rate. Because the baud rate (default set to 115200 bits/s) is much slower than the clock speed the modules are using (31 MHz), it is necessary to use FIFOs to prevent the loss of data.

Figure 12 - com\_module block diagram

#### 4.2.1 com\_module\_reg

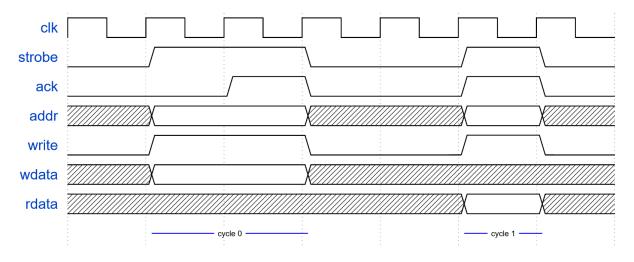

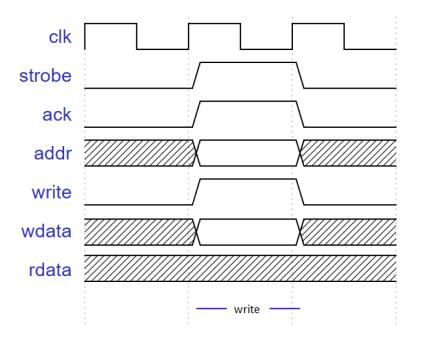

Com\_module\_reg is the component that handles the signals between the IPbus interface and any given com\_module. The goal was to make com\_module a "zero wait state"-slave, meaning that it can receive or transmit data on every clock cycle. Figure 13 shows two write transactions between IPbus and two slaves. The slave written to in cycle 0 is what is referred to as a "one wait state"-slave. It uses one clock cycle before it responds with *ipb\_ack*. IPbus is made in a way that the slave can have multiple wait states. IPbus will wait for ack before proceeding. Cycle 1 shows a slave with zero wait states. These types of slaves are the most efficient ones because they never require IPbus to wait for a response.

Figure 13 - IPbus wait state slaves

To make "zero wait state"-slaves, it was necessary to have the *ipb\_ack* mirror the *ipb\_strobe*. In the first iteration, *ack* was given *strobe*'s value directly. But because of the way ipbus\_fabric\_sel (Figure 9 ) handles the *ack*-signal, it had to be given its value via a MUX like this:

#### Listing 2 - How ACK follow strobe

The first plan was to make one process for both read- and write operations. This would cause the slave to require one wait state on every read operation because they both would be following the clock. Therefore, it has separate read and write processes.

#### **IPbus read transaction**

The signal diagram in Figure 14 shows a read transaction with a com\_module\_reg. The communication is made possible by reacting to every signal coming from IPbus. In a read transaction between IPbus and a zero-wait state slave, IPbus will change the signals going to the slave on one clock cycle. The slave can then interpret these signals and change *rdata*'s value accordingly. IPbus will then read from *rdata* on the next clock cycle.

Figure 14 – zero-wait state read

The p\_read process monitors every signal inside IPBUS\_IN and reacts if any of them change. If *strobe* is high and *write* is low, *DATA* is written to *rdata* for the IPbus to read.

```

p_read : process(IPBUS_IN) -- Module writes data to IPBUS

begin

IPBUS_OUT.ipb_rdata <= (others => '0');

if IPBUS_IN.ipb_strobe = '1' and IPBUS_IN.ipb_write = '0' then

IPBUS_OUT.ipb_rdata <= DATA;

end if; -- STROBE & READ & MODULE_ADDRESS

end process p_read;

```

Listing 3 - IPbus slave - read process

Design

#### **IPbus write transaction**

The timing in the write transaction in Figure 15 is synchronized with the clock. The slave checks if *strobe* and *write* are high on every rising edge of the clock. If so, it reads the data from *wdata*.

Figure 15 – zero-wait state write

```

p_write : process(CLK) -- Module reads data from IPBUS

begin

if rising_edge(CLK) then

if RST = '1' then

else

if IPBUS_IN.ipb_strobe = '1' and IPBUS_IN.ipb_write = '1' then

DATA <= IPBUS_IN.ipb_wdata;

end if; -- STROBE & WRITE & MODULE_ADDRESS

end if; -- RST

end if; -- CLK

end process p_write;

```

*Listing 4 - IPbus slave -write process*

The process p\_write also includes the reset signal to make sure this only happens on a rising edge of the clock.

#### Address map

As already mentioned, *ipb\_addr(7 downto 0)* from IPbus is available for selecting internal registers inside the modules. Com\_module\_reg takes care of this selection. Table 1 shows the address map of a com\_module. The first two registers are reserved as control and status. Nothing is implemented here, as there was no need to do so. This was just a habit from earlier designs and makes it easier to implement more features later if needed. The data written to register 3 is sent to com\_module\_usart through one of the FIFOs and further down towards the power control units. Register 4 holds the data received by the power control units. Register 5 is a trigger register that resets both FIFOs. It does not matter if the data sent to register 5 is all zeros or all ones, everything is considered a reset if the register is reached.

| Name                                    | Register<br>address | Width | Access | Default Value | Description                                                                                                                                                                          |  |

|-----------------------------------------|---------------------|-------|--------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| COM_MODULE (module address 0x01 – 0x40) |                     |       |        |               |                                                                                                                                                                                      |  |

| CONTROL                                 | 0x01                | 32    | W      | 0x00          | Not in use                                                                                                                                                                           |  |

| STATUS                                  | 0x02                | 32    | R      | 0x00          | <ul> <li>[314] Not in use</li> <li>[3] TX is full (1 = full)</li> <li>[2] TX is empty (1 = empty)</li> <li>[1] RX is full (1 = full)</li> <li>[0] RX is empty (1 = empty)</li> </ul> |  |

| WRITE                                   | 0x03                | 32    | W      | 0x00          | Writes data to the corresponding PCU.<br>[31] R/W bit towards PCU<br>[3024] Not in use<br>[2316] PCU reg address<br>[120] Data to PCU                                                |  |

| READ                                    | 0x04                | 32    | R      | 0x00          | Reads a 32-bit vector from the corresponding<br>PCU.<br>[31] R/W bit towards PCU<br>[3024] Not in use<br>[2316] PCU reg address<br>[120] Data from PCU                               |  |

| RESET_FIFO                              | 0x05                | 32    | W      | 0x00          | Resets both TX and RX FIFO to clear them.                                                                                                                                            |  |

Table 2 - address map com\_module

One of the goals with com\_module\_reg was to make the code behind the address map easy to understand and modify for future use. That's why both *p\_read* and *p\_write* have a case statement, shown underneath, to interpret *ipb\_addr(7 downto 0)*. To add more registers, simply add one or more lines with "*when X*".." => " in either or both *p\_read* or *p\_write* depending on if the register should be read-only, write-only or read/write.

```

case IPBUS_IN.ipb_addr(7 downto 0) is

when c_CONTROL =>

when c_STATUS =>

when c_WRITE =>

when c_READ =>

when c_RESET => -- RESET FIF0

when others =>

end case; -- REGISTER

```

Listing 5 - IPbus slave - address map

#### 4.2.2 com\_module\_fifo

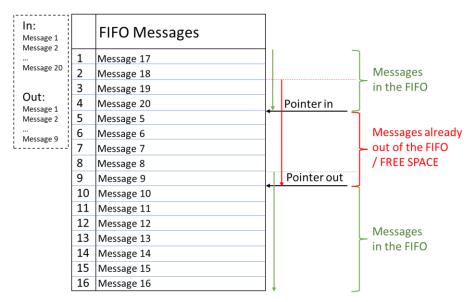

The FIFO is an acronym for "First In First Out". The main and only purpose of a FIFO is to act as a temporary backed up data storage. We decided to use a pointer-based design. Using two pointers that are moving through a list of saved messages as they are written or read. Where one of them is responsible to read and the other one to write to their current location. An example of this is illustrated in Figure 16 and Figure 17. In Figure 16 there have been eight messages sent into the FIFO, two of these messages have then been read. That means that there are now six messages in the FIFO, messages three through eight. In Figure 17, another twelve messages have been sent into the FIFO, and now a total of nine messages have been read. At this point, messages ten through twenty are still in the FIFO, and one through nine are out. This shows how the "pointer in" has moved through the whole list and moved back to the start, but it isn't a problem because enough messages have already been read. The place where messages five through nine were stored is now "free space".

| In:<br>Message 1 |    | FIFO Messages |             | Messages already |

|------------------|----|---------------|-------------|------------------|

| Message 2<br>    | 1  | Message 1     |             | out of the FIFO  |

| Message 8        | 2  | Message 2     | Pointer out | / FREE SPACE     |

| Out:             | 3  | Message 3     | -           |                  |

| Message 1        | 4  | Message 4     |             |                  |

| Message 2        | 5  | Message 5     |             | Messages         |

|                  | 6  | Message 6     |             | in the FIFO      |

| l                | 7  | Message 7     |             |                  |

|                  | 8  | Message 8     | Pointer in  |                  |

|                  | 9  |               |             |                  |

|                  | 10 |               |             |                  |

|                  | 11 |               |             |                  |

|                  | 12 |               |             |                  |

|                  | 13 |               |             |                  |

|                  | 14 |               |             |                  |

|                  | 15 |               |             |                  |

|                  | 16 |               |             |                  |

Figure 16 - part one in a pointer-based FIFO illustration.

Figure 17 – part two in a pointer-based FIFO illustration.

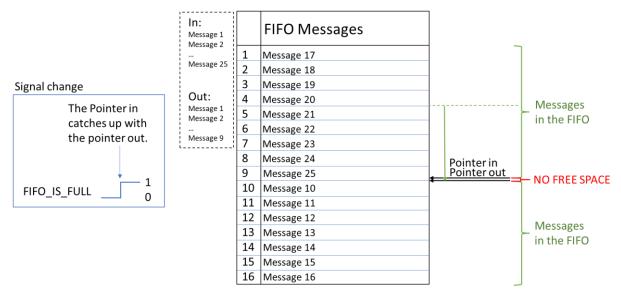

There are some important corner cases to take into consideration when working with a FIFO. First and foremost, you will encounter one of these if you only write messages into the FIFO, but never read any out. This will end up in the FIFO being full. In this case, this FIFO will not accept any more messages, and any message that is still trying to get in will just be forgotten. However, when this happens the signal FIFO\_IS\_FULL, which is an output, will be set to 1. This corner case is illustrated in Figure 18.

Figure 18 - part three in a pointer-based FIFO illustration.

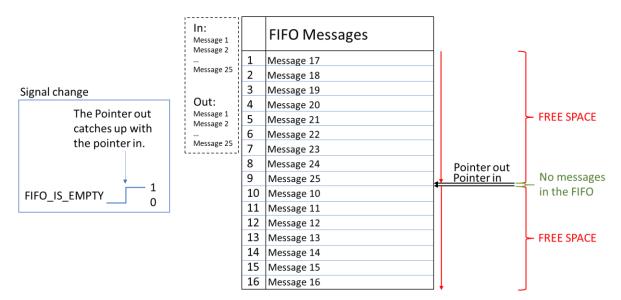

Another corner case to take into consideration is what happens if you only try to read from the FIFO. At some point, there will be no more messages inside, and the FIFO will be empty. In this case, the FIFO will return only 0. As well as when full, there is an out signal "FIFO\_IS\_EMPTY" that is set to 1 when this corner case is hit. Illustration of this case in Figure 19.

Figure 19 - part four in a pointer-based FIFO illustration.

#### 4.2.3 com\_module\_usart

The main part of the com\_module is the com\_module\_usart. This part is responsible for the communication between the MJCU and the PCUs. When it came to choosing how to design this component, the choice was very clear. In earlier subjects in our study, we have had multiple experiences with state machines. So, it felt natural to choose a state-machine solution for the design.

The TX\_FIFO sends out one 32-bit message at a time every time the com\_module\_usart tells it to do so. The FIFO has two additional information outputs, "FIFO\_IS\_EMPTY" and "FIFO\_IS\_FULL". The component continuously tells the FIFO to send out a new message as long as "FIFO\_IS\_EMPTY" is false. This is to make the component as time efficient as possible.

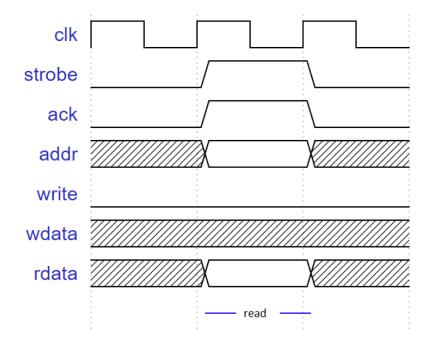

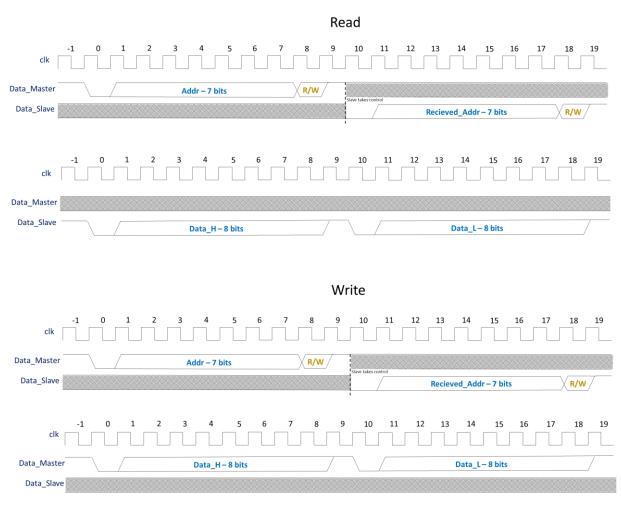

In Figure 20 a signal diagram is showing the protocol that is used for communicating. Starting every transaction with an initializing bit where high goes to low. A 7-bit address is sent followed by a R/W bit. Then for every read or write transaction a handshake is sent. The handshake is just the slave repeating what it has just received. Depending on if it is a read or a write, either master or slave then proceeds to send its data.

Figure 20 - Custom USART protocol between the FPGA and PCUs

#### The state machine

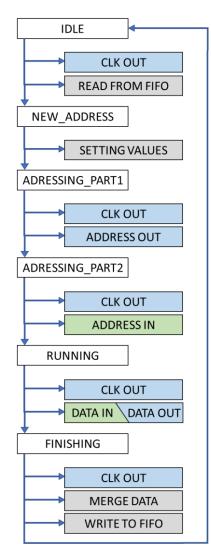

The state machine contains the following states: IDLE, NEW\_ADDRESS, ADDRESSING\_PART1, ADDRESSING\_PART2, RUNNING, FINISHING.

Figure 21 – The state machine in com\_module\_usart.

The component will be in IDLE until FIFO\_IS\_EMPTY goes from 1 to 0. Then it moves into NEW\_ADDRESS to set up all the different signals and reset the counters. After this state was created, the next part was to figure out how to do the transaction itself. There is one master (com\_module\_usart) and one slave (PCU). The serial transaction is split into 3 parts.

The first part is the master writing to the slave which one of the internal registers of the PCU it wants to read or write to. Then in part two, the slave responds with the same read/writebit and register address that it received from the master. This is called a handshake. With a handshake, the master can be certain that the correct address has been reached, and that the slave is active and responding correctly. When the handshake is received, the next part depends on if the message is a "read" or a "write". In both cases, 16 bits split into two chunks of 8 bits will be transferred between master and slave. When it is a "read" that is being executed, the slave will know, because of the read/write-bit, to write its data to the bus, and the master will read it. When a "write" is being executed, the master sends data to the bus, and the slave reads.

This sequence contains the states ADDRESSING\_PART1, ADDRESSING\_PART2, and RUNNING.

ADDRESSING\_PART1 takes care of sending the read/write-bit and the register address.

ADDRESSING\_PART2 reads the read/write-bit and the address that the slave responds with.

RUNNING includes both the "read" and "write" sequences. *Read* reads 16 bits from the slave and *write* writes 16 bits to the slave. The read/write-bit that was sent during the ADDRESSING\_PART1 decides which one of the two sequences to run. Either way, the whole RUNNING state must get through the same number of bits. This means that the only thing that changes is whether to write to the slave or to read from the slave.

Then there is one more state, FINISHING. This state serves the purpose of delivering the data package to the RX\_FIFO and telling the TX\_FIFO that it is ready for the next transaction.

Then it switches back to IDLE.

While all this is happening, a 32-bit vector is constructed in the same format as the one read from the TX\_FIFO. This data package includes if it was a read or write that was executed, what register it spoke with, and the data received/sent.

There is one more important part. Because this is USART, it needs an additional clock signal to synchronize the data transfer. There is a separate process that takes care of the USART clock signal. This signal is generated at a given baud rate that is controlled by the global\_module. The main process that handles the communication follows this signal when writing or reading.

#### How the data is read

In all parts of the state machine where data is being read or written, it is only one bit at a time. This means that the serial data that goes in or out needs to be converted to a vector at some point. This is solved by using a counter that iterates through a vector and writes one bit at a time into the vector. It would have been more space-efficient to use a shift register rather than a pointer-based design. A shift register uses as many flip-flops as there are bits in the vector. This is not a problem for this project because the FPGA is as big as it is. The pointer-based design gave options for easy modification while developing. Coincidentally this ended up being very useful. The reason is that there was some confusion regarding if the most significant bit should come first or the least significant bit. In the end, the data needed to be flipped. All data transactions in the USART are LSB to MSB as of the current version.

## 4.3 global\_module

The global\_module is just a modified com\_module\_reg with a couple more outputs towards the com\_modules. The first two registers are reserved to control and status. Nothing is implemented here, as there was no need to do so. This was just a habit from earlier designs and makes it easier to add more features in the future if needed. The data written to register 3 is sent to every com\_module in the system. This makes use of a big advantage the FPGA has over a standard computer or an MCU. Since all com\_modules get the same message, they can begin communicating with all power control units at the same time. In other words, communicating with one PCU takes the same amount of time as communicating with all of them. Register 4 does not do anything because this module never gets any of the data from the PCUs. Writing to register 5 will reset all other modules. This includes resetting the FIFOs inside every com\_module. Register 6 and 7 are used to control the baud rate between the com\_modules and PCUs. Write these values in binary, and they will be converted internally.

| Name                                | Register<br>address | Width | Access | Default Value | Description                                                                                                                                                                     |  |

|-------------------------------------|---------------------|-------|--------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| GLOBAL_MODULE (module address 0x00) |                     |       |        |               |                                                                                                                                                                                 |  |

| GLOBAL_CONTROL                      | 0x01                | 32    | W      | 0x00          | Not in use                                                                                                                                                                      |  |

| GLOBAL_STATUS                       | 0x02                | 32    | R      | 0x00          | Not in use                                                                                                                                                                      |  |

| GLOBAL_WRITE                        | 0x03                | 32    | W      | 0x00          | Writes data to every com_module in the system.<br>[31] R/W bit towards PCU<br>[3024] Not in use<br>[2316] PCU reg address<br>[120] Data to PCU                                  |  |

| GLOBAL_RESET                        | 0x05                | 32    | W      | 0x00          | Resets all modules except the global_module                                                                                                                                     |  |

| COM_ENABLE_0                        | 0x06                | 32    | R/W    | OxFFFFFFF     | These 32 bits enable com_modules[1→32]<br>'1' = ENABLED<br>Bit[n] controls com _module_[1+n]<br>This function is made in the case that modules<br>are not connected to a PCU.   |  |

| COM_ENABLE_1                        | 0x07                | 32    | R/W    | OxFFFFFFF     | These 32 bits enable com_modules[33→64]<br>'1' = ENABLED<br>Bit[n] controls com _module_[33+n]<br>This function is made in the case that modules<br>are not connected to a PCU. |  |

| SYSTEM CLOCK<br>SPEED               | 0x08                | 32    | R/W    | 0x1D905C0     | The speed of the clock used by the<br>com_modules.<br>This is used to calculate the baud rate towards<br>the PCUs.<br>Default: 31Mhz (clock from IPbus)                         |  |

| PSU BAUD RATE                       | 0x09                | 32    | R/W    | 0x1C200       | The baud rate to use towards the PCUs                                                                                                                                           |  |

Table 3 - Address map global\_module

## 4.4 dummy\_module

Dummy\_module is the simplest module, and it was also the first one to be completed. After the creation of com\_module\_reg, one signal was added to store a 32-bit vector. The thought behind having a dummy\_module is to make sure the communication between IPbus SW and an IPbus HW-slave works properly. Write something to register 3 and it can be read back from register 4.

| Name                               | Register<br>address | Width | Access | Туре | Default Value | Description                         |  |

|------------------------------------|---------------------|-------|--------|------|---------------|-------------------------------------|--|

| DUMMY_MODULE (module address 0x43) |                     |       |        |      |               |                                     |  |

| WRITE                              | 0x03                | 32    | W      | STAT | 0x00          | Write anything to store a new value |  |

| READ                               | 0x04                | 32    | R      | STAT | 0xDEADBEEF    | Read back the stored value          |  |

Table 4 - Address map dummy\_module

#### 4.5 version\_module and housekeeping\_module